**Enabling Energy Efficient Solutions**

www.onsemi.com

#### **ON Semiconductor**<sup>®</sup>

# Design of a QR Adapter with Improved Efficiency and Low Standby Power

# Agenda

- 1. Quasi-Resonance (QR) Generalities

- 2. The Valley Lockout Technique

- 3. The NCP1379/1380

- 4. Step by Step Design Procedure

- Performances of a 60 W Adapter Featuring Valley Lockout

# Agenda

- 1. Quasi-Resonance (QR) Generalities

- 2. The Valley Lockout Technique

- 3. The NCP1379/1380

- 4. Step by Step Design Procedure

- 5. Performances of a 60 W Adapter Featuring Valley Lockout

#### What is Quasi-Square Wave Resonance ?

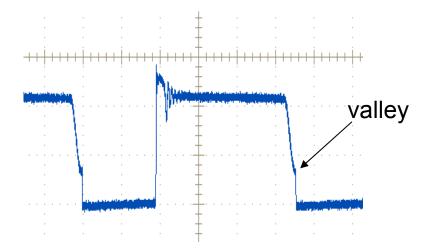

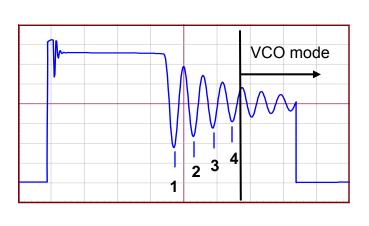

- MOSFET turns on when  $V_{DS}(t)$  reaches its minimum value.

- Minimizes switching losses

- Improves the EMI signature

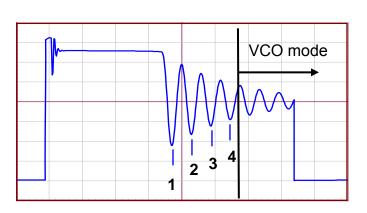

MOSFET turns on in first valley

MOSFET turns on in second valley

N Semiconductor\*

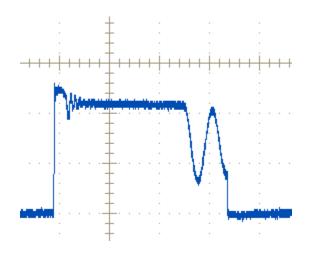

#### **Quasi-Resonance Operation**

- In DCM,  $V_{DS}$  must drop from  $(V_{in} + V_{reflect})$  to  $V_{in}$

- Because of  $L_p$ - $C_{lump}$  network  $\rightarrow$  oscillations appear

- Oscillation half period:  $t_x = \pi \sqrt{L_p C_{lump}}$

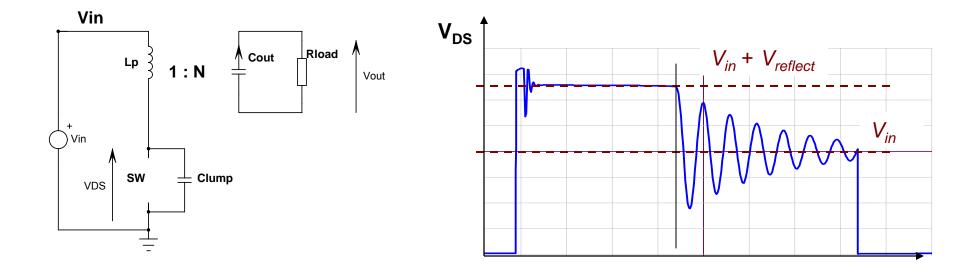

#### A Need to Limit the Switching Frequency

• In a self-oscillating QR,  $F_{sw}$  increases as the load decreases

Higher losses at light load if  $F_{sw}$  is not limited

- 2 methods to limit  $F_{sw}$ :

- Frequency clamp with frequency foldback

- Changing valley with valley lockout

#### **Frequency Clamp in QR Converters**

□ In light load, frequency increases and hits clamp

- Multiple valley jumps

- Jumps occur at audible range

- Creates signal instability

ÛN

# Agenda

- 1. Quasi-Resonance (QR) Generalities

- 2. The Valley Lockout Technique

- 3. The NCP1379/1380

- 4. Step by Step Design Procedure

- 5. Performances of a 60 W Adapter Featuring Valley Lockout

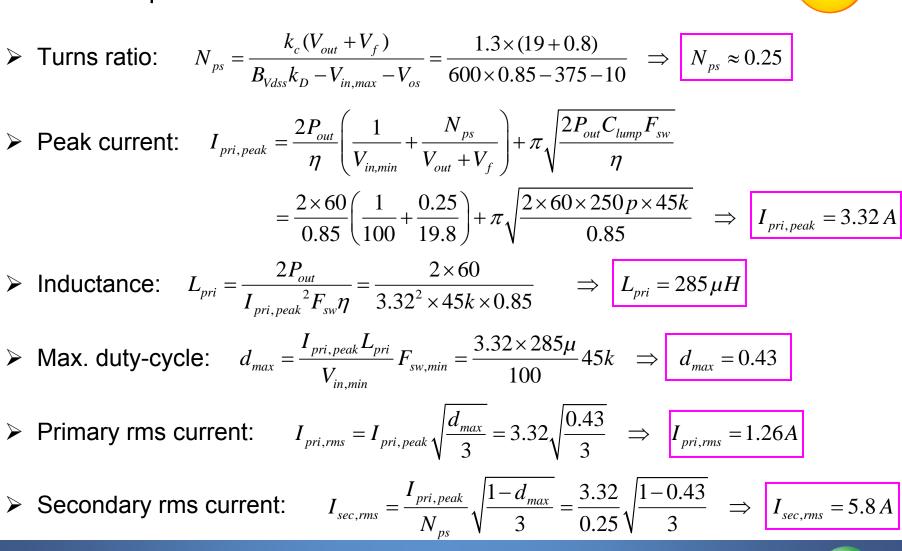

## **The Valley Lockout**

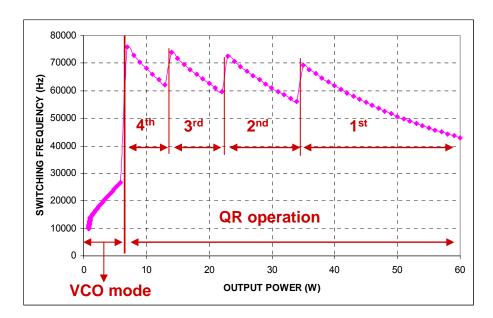

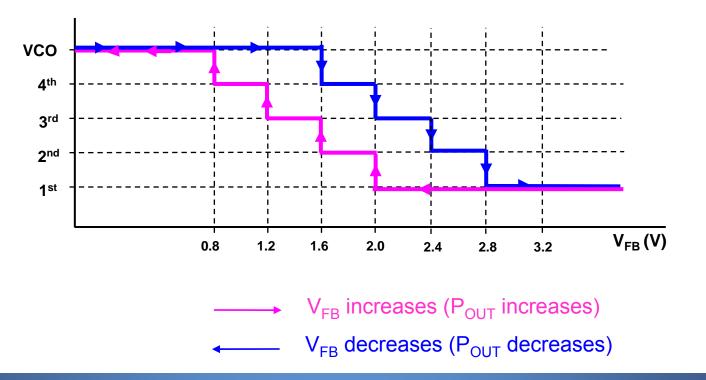

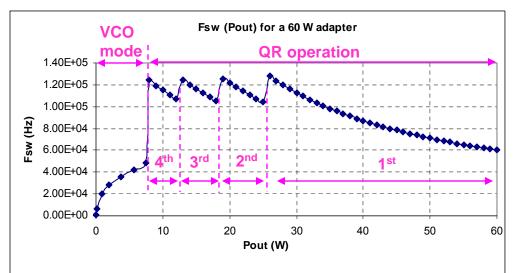

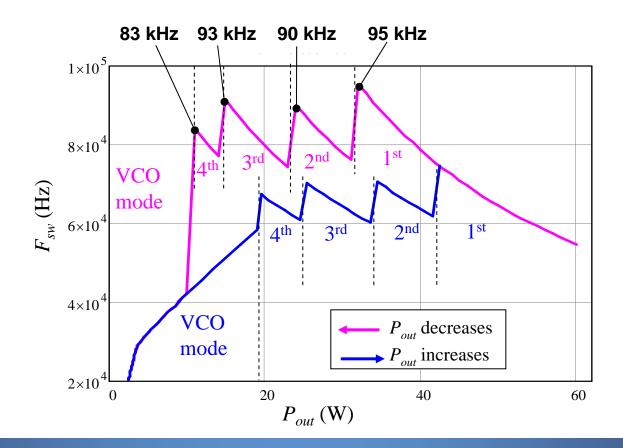

- As the load decreases, the controller changes valley (1<sup>st</sup> to 4<sup>th</sup> valley in NCP1380)

- The controller stays locked in a valley until the output power changes significantly.

- No valley jumping noise

- Natural switching frequency limitation

## **The Valley Lockout**

- FB comparators select the valley and pass the information to a counter.

- The hysteresis of FB comparators locks the valley.

- 2 possible operating set points for a given FB voltage.

# Agenda

- 1. Quasi-Resonance (QR) Generalities

- 2. The Valley Lockout Technique

- 3. The NCP1379/1380

- 4. Step by Step Design Procedure

- 5. Performances of a 60 W Adapter Featuring Valley Lockout

## NCP1379/1380 Features

- Operating modes:

- QR current-mode with valley lockout for noise immunity

- VCO mode in light load for improved efficiency

- Protections

- Over power protection

- Soft-start

- Short circuit protection

- Over voltage protection

- Over temperature protection

- Brown-Out

□ Mass production: Q4 2009

## **QR Mode with Valley Lockout**

#### • Operating principle:

- Locks the controller into a valley (up to the 4<sup>th</sup>) according to FB voltage.

- Peak current adjusts according to FB voltage to deliver the necessary output power.

#### Advantages

- Solves the valley jumping instability in QR converters

- Achieves higher min  $F_{sw}$  and lower max  $F_{sw}$  than in traditional QR converters

- Reduce the transformer size

ON Semiconductor\*

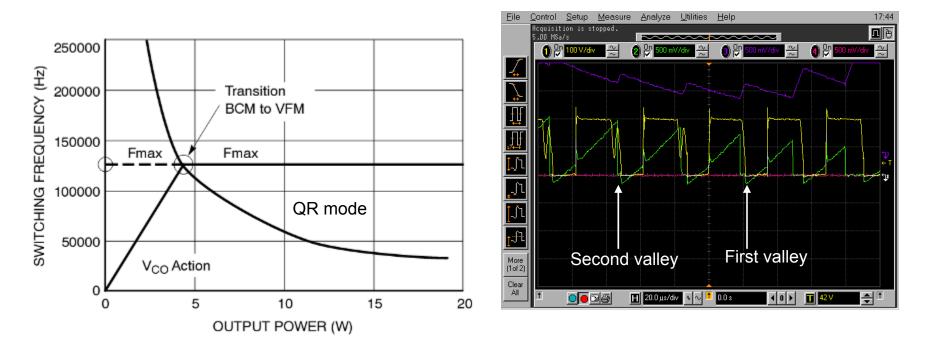

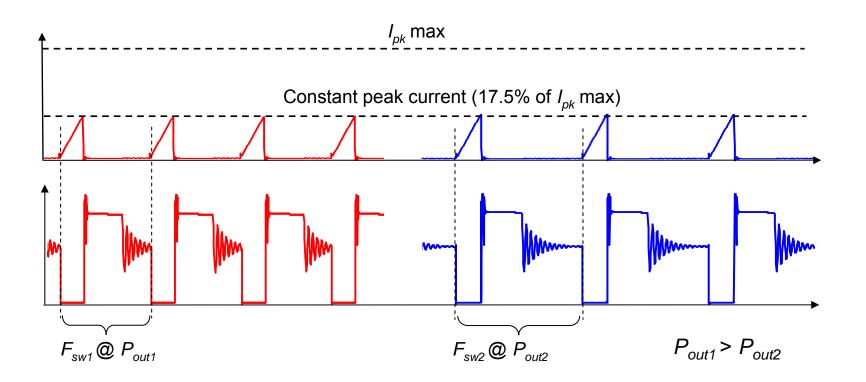

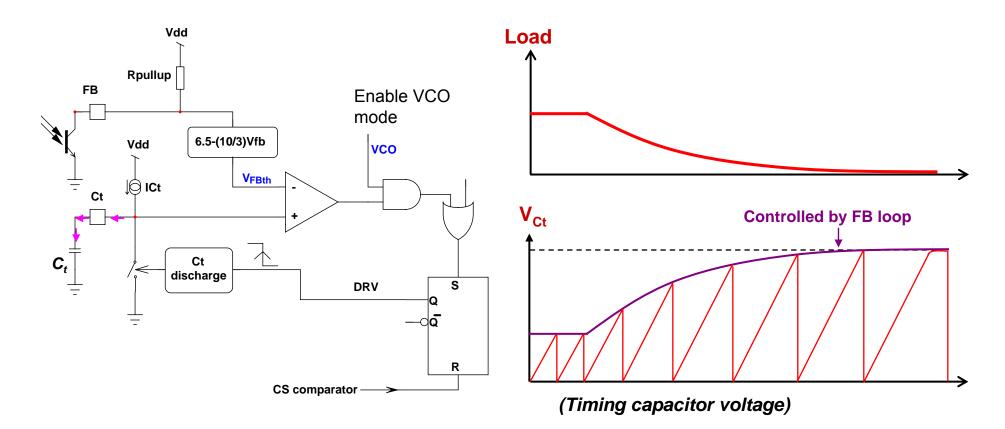

## **VCO Mode**

- Occurs when  $V_{FB} < 0.8 \text{ V} (P_{out} \text{ decreasing}) \text{ or } V_{FB} < 1.4 \text{ V} (P_{out} \text{ increasing})$

- Fixed peak current (17.5% of  $I_{pk,max}$ ), variable frequency set by the FB loop.

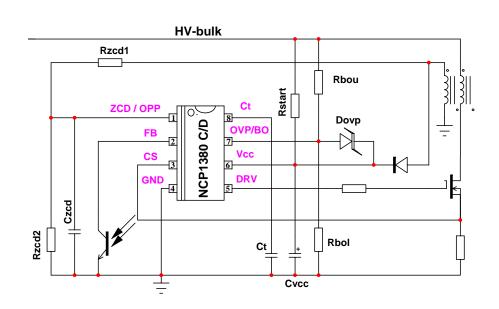

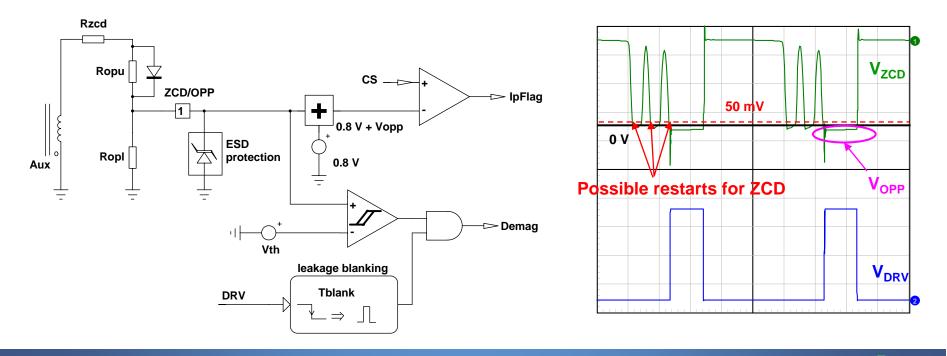

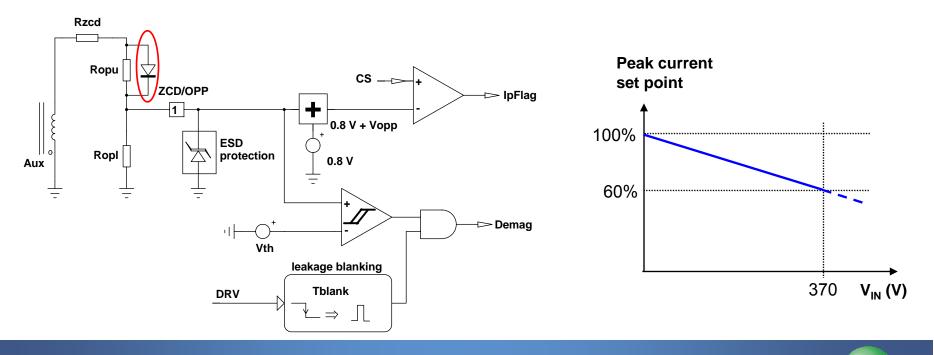

## **Combined ZCD and OPP**

- Zero-Crossing Detection (ZCD) and Over Power Protection (OPP) are achieved by reading the Aux. winding voltage

- ZCD function used during the off-time of MOSFET (positive voltage).

- OPP function used during the on-time of MOSFET (negative voltage)

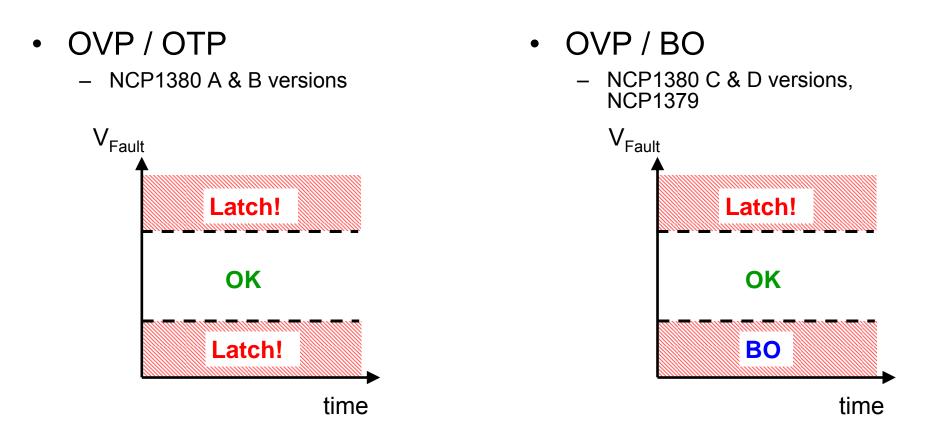

#### **NCP1380 Versions**

• 4 versions of NCP1380: A, B, C and D

|                | ОТР | OVP | во | Auto-Recovery<br>Over current protection | Latched<br>Over current protection |

|----------------|-----|-----|----|------------------------------------------|------------------------------------|

| NCP1380 /<br>A | X   | X   |    |                                          | X                                  |

| NCP1380 /<br>B | x   | X   |    | X                                        |                                    |

| NCP1380 /<br>C |     | X   | X  |                                          | X                                  |

| NCP1380 /<br>D |     | X   | X  | X                                        |                                    |

**OTP**: Over Temperature Protection **OVP**: Over Voltage Protection **BO**: Bown-Out

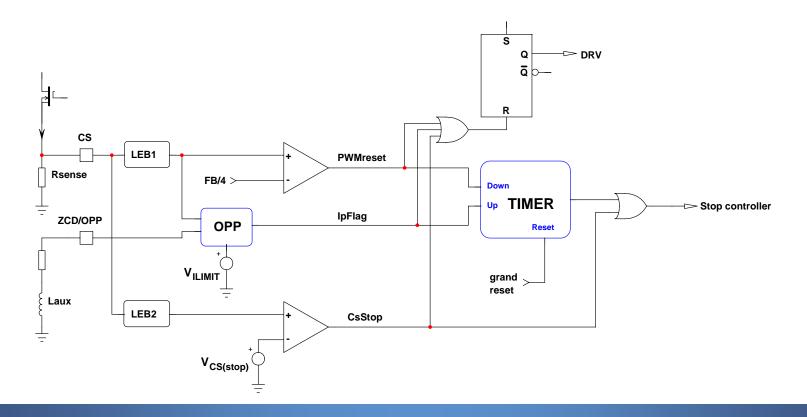

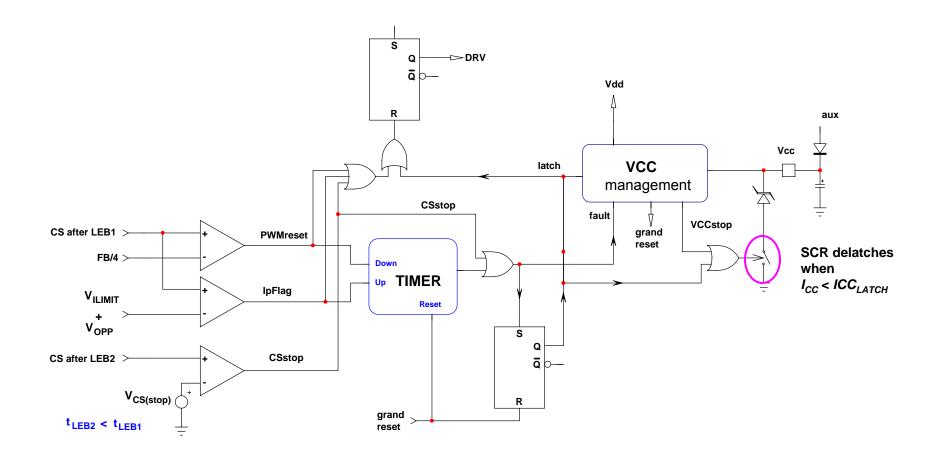

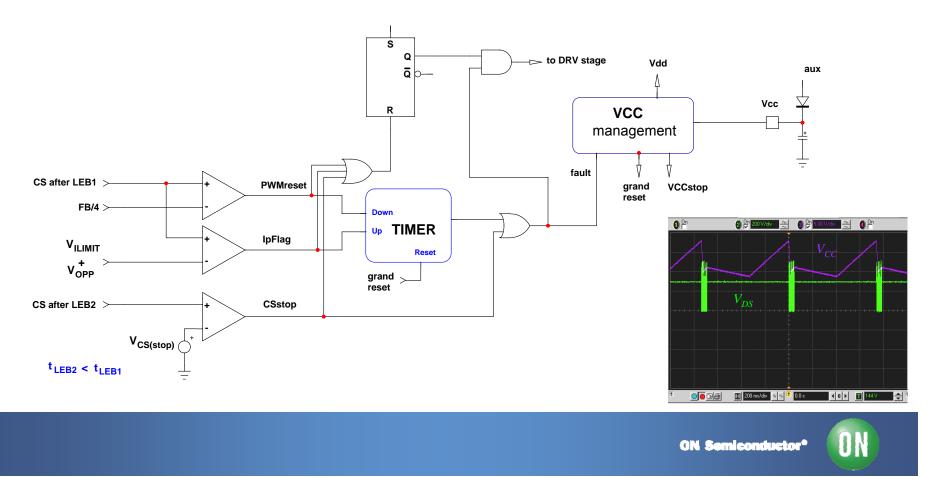

#### **Short-Circuit Protection**

- Internal 80 ms timer for short-circuit validation.

- Additional CS comparator with reduced LEB to detect winding short-circuit.

- $V_{CS(stop)} = 1.5 * V_{ILIMIT}$

#### **Short-Circuit Protection (A and C versions)**

- A and C versions: the fault is latched.

- $-V_{CC}$  is pulled down to 5 V and waits for ac removal.

## Short Circuit Protection (B and D)

- Auto-recovery short circuit protection: the controller tries to restart

- Auto-recovery imposes a low burst in fault mode.

Low average input power in fault condition

## **Fault Pin Combinations**

- OVP and OTP or OVP and BO combined on one pin.

- Less external components needed.

ON Semiconductor\*

# Agenda

- 1. Quasi-Resonance (QR) Generalities

- 2. The Valley Lockout Technique

- 3. The NCP1379/1380

#### 4. Step by Step Design Procedure

5. Performances of a 60 W Adapter Featuring Valley Lockout

## **Step by Step Design Procedure**

- Calculating the QR transformer

- Predicting the switching frequency

- Implementing Over Power Compensation

- Improving the efficiency at light load with the VCO mode

- Choosing the startup resistors

- Implementing synchronous rectification

## **Design Example**

• Power supply specification:

$$V_{out} = 19 V$$

$$P_{out} = 60 \text{ W}$$

- $F_{sw,min} = 45 \text{ kHz} (at V_{in} = 100 \text{ Vdc})$

- 600 V MOSFET

– Standby power consumption < 100 mW @ 230 Vrms

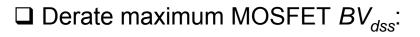

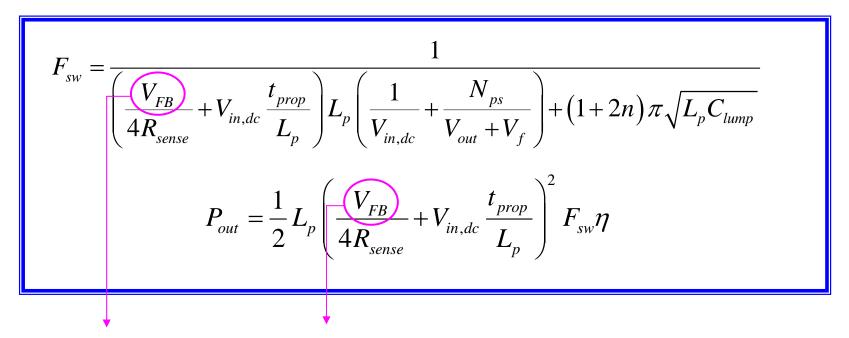

#### **Turns Ratio Calculation**

$V_{ds,max} = BV_{dss}(k_D) - k_D$ : derating factor

□ For a maximum bulk voltage, select the clamping voltage:

$V_{clamp} = V_{ds,max} - V_{in,max} - V_{os}$ V<sub>os</sub>: diode overshoot

Deduce turns ratio:

$$N_{ps} = \frac{N_s}{N_p} = \frac{k_c (V_{out} + V_f)}{V_{clamp}}$$

$$k_c: \text{ clamping coef.}$$

$$k_c = V_{clamp} / V_{reflect}$$

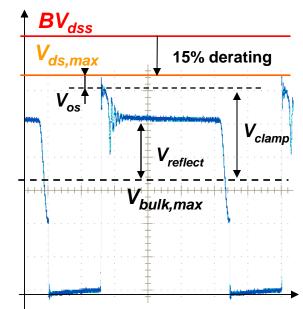

# How to Choose k<sub>c</sub>

- $k_c$  choice dependent of  $L_{leak}$  (leakage inductance of the transformer)

- *k<sub>c</sub>* value can be chosen to equilibrate MOS conduction losses and clamping resistor losses.

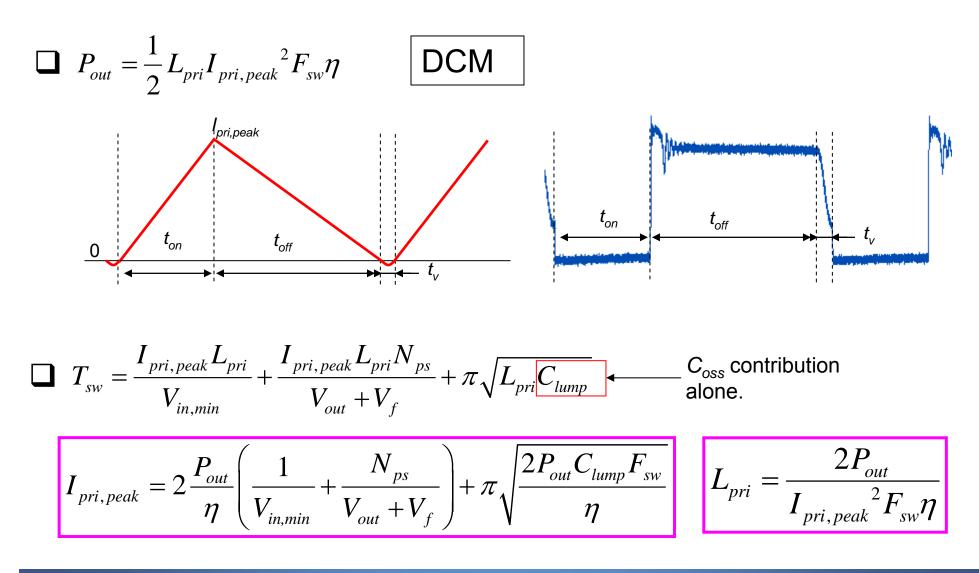

#### **Primary Peak Current and Inductance**

## **RMS Current**

• Calculate maximum duty-cycle at maximum  $P_{out}$  and minimum  $V_{in}$ :

$$d_{max} = \frac{I_{pri, peak} L_{pri}}{V_{in, min}} F_{sw, min}$$

• Deduce primary and secondary RMS current value:

## **Design Example**

Based on equations from slides 11 to 14:

0

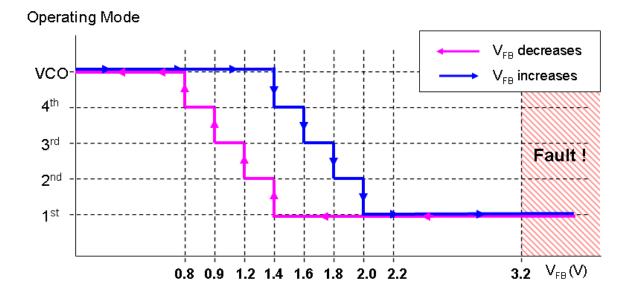

## **Predicting the Switching Frequency**

- The controller changes valley as the load decreases.

- => How can we predict the switching frequency evolution as the load varies ?

Depending upon the power increase or decrease, the FB levels at which the controller changes valley are different => valley lockout

## **Predicting the Switching Frequency**

• Knowing the FB threshold values, we can calculate  $F_{sw}$  evolution and the corresponding  $P_{out}$ .

Replace  $V_{FB}$  by the valley thresholds values in the previous slide

ON Semiconductor\*

#### **Predicting the Switching Frequency**

Calculate by hand (using the previous equations) or use the Mathcad spreadsheet to deduce the maxima of the switching frequency => EMI

**ON Semiconductor\***

## **VCO Mode**

- The switching frequency is set by the end of charge of  $C_t$  capacitor

- The end of charge of  $C_t$  capacitor is controlled by the FB loop

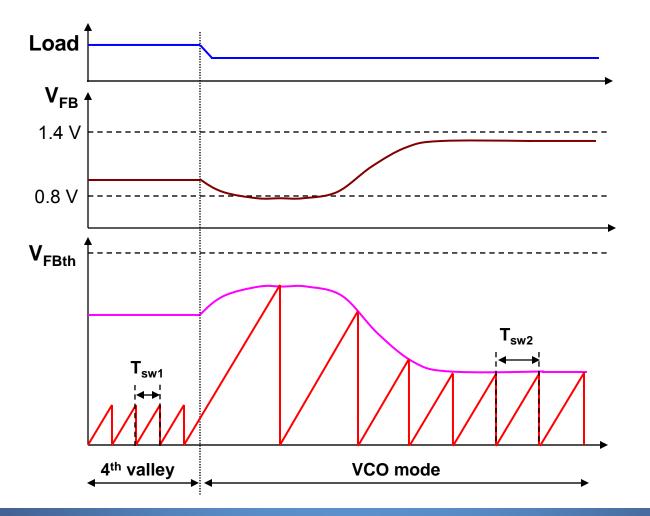

#### 4<sup>th</sup> Valley to VCO Mode Transition

• Output load slightly decreases:

#### How to Calculate C<sub>t</sub> Capacitor ?

• Switching frequency at the end of the 4<sup>th</sup> valley operation ( $V_{FB} = 0.8$  V):

$$T_{sw,4th-VCO} = \left(\frac{0.8}{4R_{sense}} + t_{prop} \frac{V_{in,max}\sqrt{2}}{L_p}\right) L_p \left(\frac{1}{V_{in,max}\sqrt{2}} + \frac{N_{ps}}{V_{out} + V_f}\right) + 7\pi\sqrt{L_p C_{OSS}}$$

•  $T_{sw}$  gap between 4<sup>th</sup> valley and VCO mode must not exceed **10 µs** (based on lab experiments) for  $V_{FB}$  = 1.4 V (hysteresis):

$$T_{sw,VCO} = T_{sw,4th-VCO} + 10 \ \mu s$$

• The relationship between  $V_{FB}$  and  $V_{Ct}$  is:

$$V_{Ct} = 6.5 - (10/3)V_{FB} = 6.5 - (10/3) \times 1.4 = 1.83 \text{ V}$$

1.83

# **C**<sub>t</sub> Design Example

• Switching frequency at the end of the 4<sup>th</sup> valley operation :

$$T_{sw,4th-VCO} = \left(\frac{0.8}{4 \times 0.23} + 300n\frac{265\sqrt{2}}{285\mu}\right) 285\mu \left(\frac{1}{265\sqrt{2}} + \frac{0.25}{19 + 0.8}\right) + 7\pi\sqrt{285\mu \times 250p}$$

$$= 10.7\,\mu s$$

*T<sub>sw</sub>* gap between 4<sup>th</sup> valley and VCO mode must not exceed 10 μs (based on lab experiments):

$$T_{sw,VCO} = T_{sw,4th-VCO} + 10 \ \mu s = 10.7\mu + 10\mu = 20.7\,\mu s$$

• The timing capacitor value is:

$$C_t = \frac{I_{Ct} T_{sw,VCO}}{1.83} = \frac{20\mu \times 20.7\mu}{1.83} = 226 \, pF$$

• Finally, we choose  $C_t = 200 \text{ pF}$

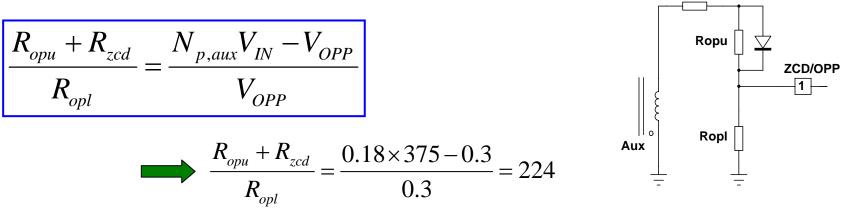

#### **OPP: How it Works ?**

- $L_{aux}$  with flyback polarity swings to  $-NV_{IN}$  during the on time.

- Adjust amount of OPP voltage with (R<sub>zcd</sub>+R<sub>opu</sub>) // R<sub>opl</sub>.

- $V_{CS,max} = 0.8 V + V_{OPP}$

- The diode bypass R<sub>opu</sub> during the off-time for optimum zero-crossing detection.

**ON Semiconductor**<sup>4</sup>

#### **OPP Amount Needed for the Design**

• Because of the propagation delay, at high line:

• The switching frequency is:

$$T_{sw(high)} = I_{pk(high)} L_{p} \left( \frac{1}{V_{in,max} \sqrt{2}} + \frac{N_{ps}}{V_{out} + V_{f}} \right) + \pi \sqrt{L_{p} C_{lump}}$$

$$\longrightarrow T_{sw(high)} = 4.32 \times 290 \times 10^{-6} \left( \frac{1}{265\sqrt{2}} + \frac{0.25}{19 + 0.8} \right) + \pi \sqrt{285 \times 10^{-6} \times 250 \times 10^{-12}} = 19.5 \,\mu s$$

• The power capability at high line is:

$$P_{out(high)} = \frac{1}{2} L_p I_{pk(high)}^2 \frac{1}{T_{sw(high)}} \eta$$

$$P_{out(high)} = \frac{1}{2} 290 \times 10^{-6} \times 4.32^2 \frac{1}{19.5 \times 10^{-6}} 0.85 = 116 W$$

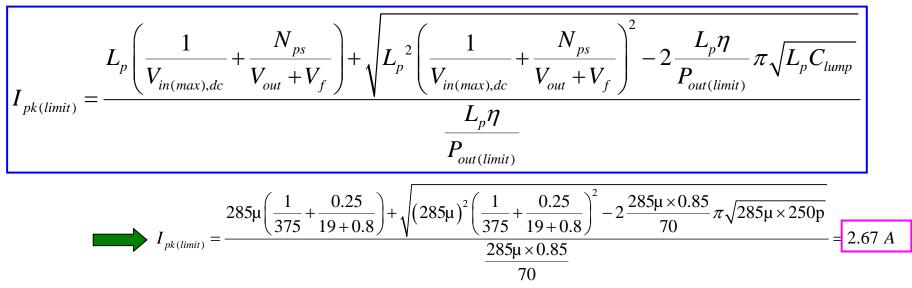

### **Amount of OPP Voltage Needed**

- Limit the output power to  $P_{out(limit)} = 70$  W at high line.

- What is the peak current I<sub>pk(limit)</sub> corresponding to P<sub>out(limit)</sub>?

Amount of OPP voltage needed:

$$V_{OPP} = 0.8 \left( 1 - \frac{I_{pk(limit)}}{I_{pk(max)}} \right)$$

$$V_{OPP} = 0.8 \left( 1 - \frac{2.67}{4.32} \right) = 300 \, mV$$

#### **Calculating the OPP Resistors**

- The amount of OPP voltage needed to limit  $P_{out}$  to 70 W is :  $V_{OPP}$  = 300 mV

- Resistor divider law:

• We choose:  $R_{opl} = 1 \text{ k}\Omega$  and  $R_{zcd} = 1 \text{ k}\Omega$

$$R_{opu} = 221R_{opl} - R_{zcd}$$

$$R_{opu} = 223k\Omega$$

Rzcd

# Why is the OPP Non Dissipative ?

- Input voltage information given by auxiliary winding

- In light load: VCO mode => T<sub>sw</sub> expands, thus the average current in the resistor bridge decreases

$$I_{bridge,avg} = \frac{1}{R_{zcd} + R_{opu} + R_{opl}} \left(\frac{t_{on}}{T_{sw}}\right) N_{p,aux} V_{IN} + \frac{1}{R_{opu} + R_{opl}} \left(\frac{t_{off}}{T_{sw}}\right) V_{CC} + V_{f} \right)$$

Previous example:  $R_{opu}$  = 220 kΩ,  $R_{opl}$  = 1 kΩ,  $R_{zcd}$  = 1 kΩ

At light load ( $P_{out}$  = 4 W),  $t_{on}$  = 1.2 μs,  $t_{off}$  = 3.6 μs,  $T_{sw}$  = 40 μs

$$I_{bridge,mean} = \frac{1}{220k + 1k + 1k} \frac{1.2\mu}{40\mu} \times 0.18 \times 375 + \frac{1}{220k + 1k} \frac{3.6\mu}{40\mu} 16 = 15 \ \mu A$$

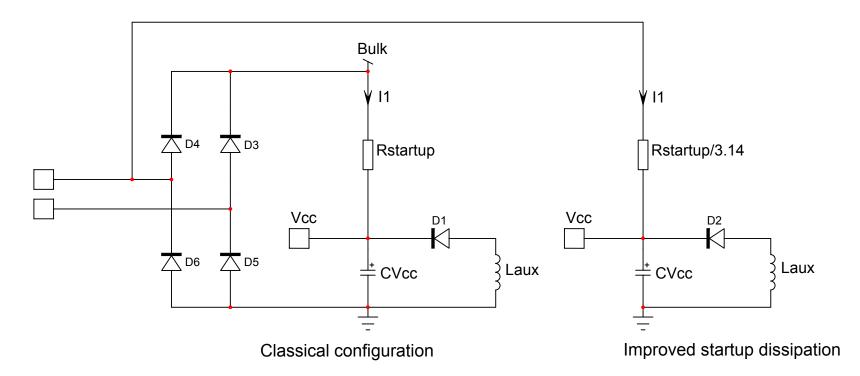

# **Startup Network**

- The startup resistor can either be connected:

- To the bulk capacitor with  $R_{startup}$

- To the half-wave for a similar charging current, take  $R_{startup}/\Pi$

ΠN

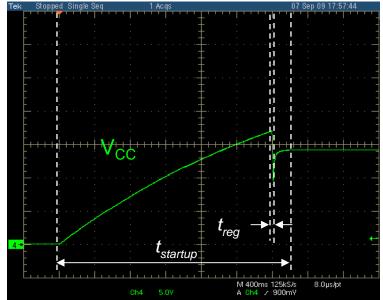

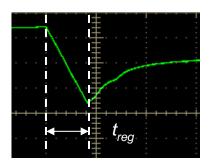

# **Startup Capacitor Calculation**

•  $C_{Vcc}$  calculated to allow the power supply to close the loop before  $V_{CC}$  falls below  $V_{CC(off)}$

$$C_{Vcc} = \frac{\left(I_{CC3A} + Q_g F_{sw}\right)t_{reg}}{V_{CC(on)} - V_{CC(off)}}$$

$$C_{Vcc} = \frac{\left(2.4m + 17n \times 45000\right) \times 10m}{17 - 9} = 3.9\,\mu F$$

We choose

$$C_{Vcc} = 4.7 \ \mu F$$

• Needed startup current to charge  $C_{Vcc}$ :

$$I_{Cvcc} = \frac{V_{CC(on)}C_{Vcc}}{t_{startup}} \qquad \qquad \blacksquare \qquad I_{Cvcc} = \frac{17 \times 4.7\mu}{2.8} = 28.5\,\mu A$$

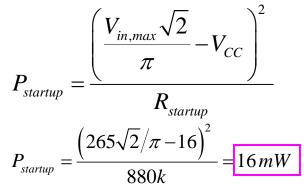

# **Startup Resistor Calculation**

- Bulk capacitor connection

- Resistor calculation:

$$R_{startup} = \frac{V_{in,min}\sqrt{2}}{I_{Cvcc} + I_{CC(start)}}$$

$$R_{startup} = \frac{85\sqrt{2}}{28.5\mu + 15\mu} = 2.76\,M\,\Omega$$

Power dissipation:

$$P_{startup} = \frac{\left(V_{in,max}\sqrt{2} - V_{CC}\right)^2}{R_{startup}}$$

$$P_{startup} = \frac{\left(265\sqrt{2} - 16\right)^2}{2.68M} = 55 \, mW$$

- Half wave connection

- Resistor calculation:

$$\frac{V_{in,min}\sqrt{2}}{R_{startup}} = \frac{\pi}{I_{Cvcc} + I_{CC(start)}}$$

$$R_{startup} = \frac{85\sqrt{2}/\pi}{28.5\mu + 15\mu} = 880 k\Omega$$

Power dissipation:

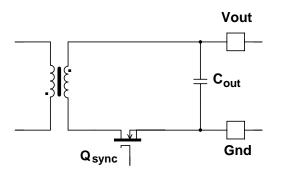

# **Synchronous Rectification**

- High rms currents in secondary side → increased losses in the output diode.

- Replace the diode with a MOSFET featuring a very low  $R_{DS(on)}$ .

| +                    | -                                                 |

|----------------------|---------------------------------------------------|

| Increased efficiency | Degraded light load and standby power consumption |

**ON Semiconductor\***

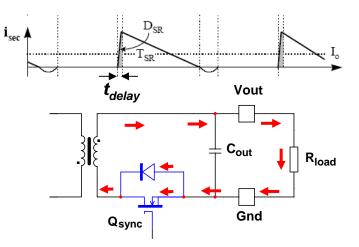

# Losses in the Sync. Rect. Switch

$$P_{Qsync} = P_{ON} + P_{Qdiode}$$

Body diode conduction losses

$P_{Qdiode} = V_f I_{out} F_{sw} t_{delay}$

MOSFET conduction losses

$$P_{ON} = R_{DS(on)120} I_{sec,rms}^{2}$$

- Body diode conducts before the MOSFET is turned-on.

- No switching losses

Losses in the Sync. Rect. switch are mainly conduction losses.

# **Choosing the Sync. Rect. MOSFET**

• Target around 1 W conduction losses in Sync. Rect. switch to avoid using an heatsink.

$$R_{DSon120} = \frac{1W}{I_{sec,RMS}^{2}}$$

$$V_{out} = 19 V$$

$$F_{sw,min} = 45 \text{ kHz}$$

Universal mains

$$R_{DSon110} = 70 \text{ m}\Omega$$

$$MBR20H150$$

$$R_{DSon110} = 50 \text{ m}\Omega$$

$$R_{DSon110} = 30 \text{ m}\Omega$$

# 60 W QR Sync. Rect. Calculations

Body diode losses:

$$P_{Qdiode} = V_f I_{out} F_{sw} t_{delay} = 0.7 \times 3.2 \times 45000 \times 70n$$

$$P_{Qdiode} = 7 \, mW$$

□ MOSFET losses:

$$P_{ON} = R_{DS(on)120} I_{sec,rms}^{2} = 30m \times 5.8^{2}$$

$$P_{ON} = 1W$$

□ Total Sync. Rect. switch losses:  $P_{Qsync} = 1 + 0.007 \approx 1W$

□ Losses into the MBR20200 diode: 2.6 W

Power loss saving: 1.6 W

# Agenda

- 1. Quasi-Resonance (QR) Generalities

- 2. The valley lockout technique

- 3. The NCP1379/1380

- 4. Step by step design procedure

- 5. Performances of a 60 W adapter featuring valley lockout

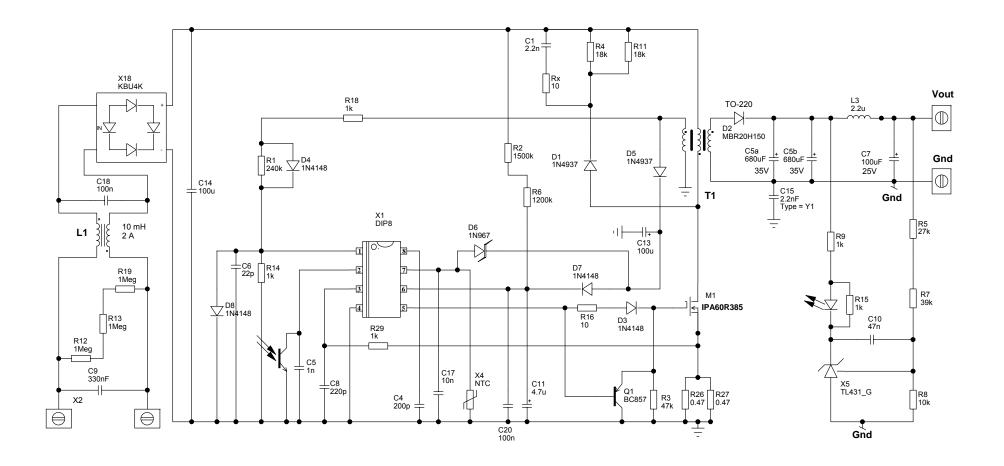

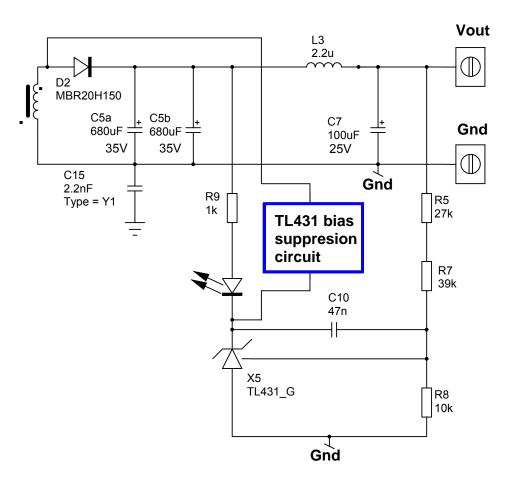

#### **60 W Demo Board Schematic**

NCP1380B in a 19 V, 60 W adapter

**ON Semiconductor\***

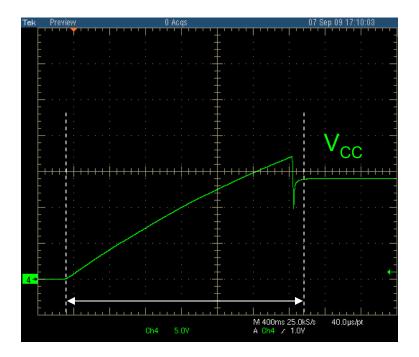

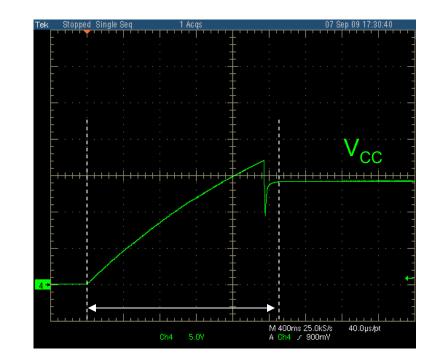

#### Startup

- Startup resistor connected to the **bulk rail** (R<sub>startup</sub> = 2.7 MΩ)

- T<sub>startup</sub> = 2.68 s

- Startup resistor connected to the half-wave (R<sub>startup</sub> = 910 kΩ)

- T<sub>startup</sub> = 2.1 s

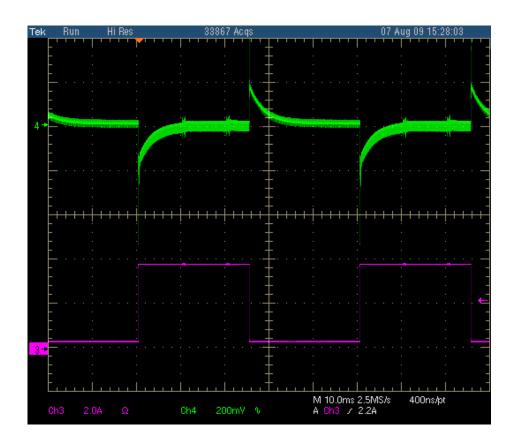

# **Transient Load Step**

Load step: 3% to 100% of output load with a slew rate of 1 A / µs

The overshoot / undershoot is 1% of the nominal value of  $V_{out}$

# **Short-Circuit**

| Tek Run  | Sample           | 10 Acqs                                | 16 Jan 09 11:03:30                       |

|----------|------------------|----------------------------------------|------------------------------------------|

|          |                  | · · · · · · · · · · · · · · · · · · ·  |                                          |

|          |                  | · · +                                  | · · · · -                                |

| F        |                  |                                        |                                          |

| · · ·    |                  | · · · · · · · · · · · · · · · · · · ·  | · · · · · · · · · · · · · · · · · · ·    |

|          |                  |                                        |                                          |

|          |                  | · · +                                  |                                          |

|          |                  | · · · · · · · · · · · · · · · · · · ·  | · · · · · · · · · · · · · · · · · · ·    |

| -        |                  | · · +                                  | · · · · -                                |

| F        |                  |                                        |                                          |

| -        |                  | · · +                                  |                                          |

|          |                  |                                        | · · · · · · · · · · · · · · · · · · ·    |

| [        | <u> </u>         |                                        | - <u>`</u>                               |

| -        |                  | · · · · · · ·                          |                                          |

|          | <del></del>      |                                        |                                          |

| E C      | · 🔥              | ·                                      |                                          |

|          |                  |                                        |                                          |

|          | C(off)           | ······································ |                                          |

|          | •                |                                        |                                          |

| -        | · ·              | · · +                                  | · · · · · -                              |

| <u> </u> | i <mark>.</mark> | · · · · · · · · · · · · · · · · · · ·  | · · · · · · · · · · · · · · · · · · ·    |

| -        | · · · · ·        | · · +                                  |                                          |

| F        |                  |                                        |                                          |

| 1.+      |                  |                                        |                                          |

| -        |                  |                                        |                                          |

| E        |                  | · · <u>+</u>                           |                                          |

|          |                  |                                        |                                          |

| Ch1 S    | 5.0V             |                                        | M 100ms 125kS/s 8.0µs/pt                 |

|          |                  | Ch4 5.0V                               | M 100ms 125kS/s 8.0µs/pt<br>A Ch4 ∿ 2.0V |

|          |                  |                                        |                                          |

- A short-circuit is made at the board output.

- The circuit pulses with a low burst (5%)

- The measured averaged input power is:  $P_{in}$  = 412.4 mW for  $V_{in}$  = 230 Vrms

# Efficiency

| 115 Vrms     |               |                     |          |  |

|--------------|---------------|---------------------|----------|--|

| $P_{out}(W)$ | $P_{out}$ (%) | P <sub>in</sub> (W) | Eff. (%) |  |

| 60.6         | 100           | 68.65               | 88.3     |  |

| 45.5         | 75            | 51.29               | 88.7     |  |

| 30.3         | 50            | 34.40               | 88.2     |  |

| 15.2         | 25            | 17.61               | 86.4     |  |

| 1.0          |               | 1.30                | 76.4     |  |

| 0.7          |               | 0.94                | 74.5     |  |

| 0.5          |               | 0.69                | 72.0     |  |

Average efficiency (25, 50, 75, 100% of P<sub>out,max</sub>): **87.9%**

| 230 Vrms     |                      |                     |          |  |

|--------------|----------------------|---------------------|----------|--|

| $P_{out}(W)$ | P <sub>out</sub> (%) | P <sub>in</sub> (W) | Eff. (%) |  |

| 60.6         | 100                  | 68.00               | 89.1     |  |

| 45.5         | 75                   | 51.43               | 88.4     |  |

| 30.3         | 50                   | 34.78               | 87.3     |  |

| 15.2         | 25                   | 17.66               | 86.1     |  |

| 1.0          |                      | 1.325               | 75.4     |  |

| 0.7          |                      | 0.958               | 73.0     |  |

| 0.5          |                      | 0.71                | 70.2     |  |

Average efficiency (25, 50, 75, 100% of P<sub>out,max</sub>): **87.7%**

# **Improving the No Load Consumption**

At very low output load, the TL431 bias is removed using a special circuit:

**ON Semiconductor\***

**ON**

# **No Load Consumption**

- *R*<sub>startup</sub> connected to the bulk rail:

- Without TL431 bias:

|                 | 115 Vrms                             | 230 Vrms                             |

|-----------------|--------------------------------------|--------------------------------------|

| $P_{out} = 0 W$ | <i>P<sub>in</sub></i> = <b>60</b> mW | <i>P<sub>in</sub></i> = <b>98</b> mW |

- With TL431 bias:

|                 | 115 Vrms                             | 230 Vrms                              |

|-----------------|--------------------------------------|---------------------------------------|

| $P_{out} = 0 W$ | <i>P<sub>in</sub></i> = <b>98</b> mW | <i>P<sub>in</sub></i> = <b>128</b> mW |

$3 M\Omega$  resistor to discharge X2 capacitor included

# **No Load Consumption**

• *R*<sub>startup</sub> connected to the half wave:

- Without TL431 bias,  $R_{startup} = 1.1 \text{ M}\Omega (T_{startup} = 2.6 \text{ s} @ 85 \text{ Vrms})$

|                 | 115 Vrms                             | 230 Vrms                             |

|-----------------|--------------------------------------|--------------------------------------|

| $P_{out} = 0 W$ | <i>P<sub>in</sub></i> = <b>55</b> mW | <i>P<sub>in</sub></i> = <b>90</b> mW |

$3 M\Omega$  resistor to discharge X2 capacitor included

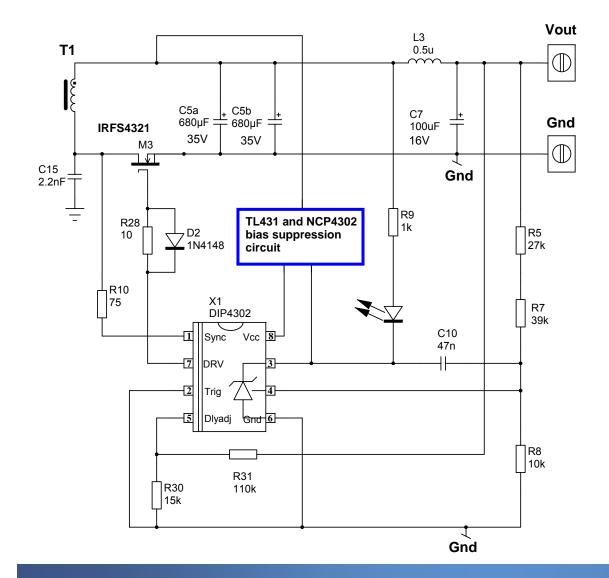

# **Synchronous Rectification Schematic**

TL431 and NCP4302 bias removed at light load.

#### **Efficiency and No Load Consumption**

|              | 115 Vi                      | rms                 |          |                      | 230 Vi               | rms                 |          |

|--------------|-----------------------------|---------------------|----------|----------------------|----------------------|---------------------|----------|

| $P_{out}(W)$ | <i>P</i> <sub>out</sub> (%) | P <sub>in</sub> (W) | Eff. (%) | P <sub>out</sub> (W) | P <sub>out</sub> (%) | P <sub>in</sub> (W) | Eff. (%) |

| 60.5         | 100                         | 67.18               | 90.1     | 60.5                 | 100                  | 66.48               | 91.0     |

| 45.4         | 75                          | 50.23               | 90.5     | 45.4                 | 75                   | 50.38               | 90.1     |

| 30.3         | 50                          | 33.78               | 89.8     | 30.3                 | 50                   | 34.2                | 88.6     |

| 15.2         | 25                          | 17.39               | 87.4     | 15.2                 | 25                   | 17.48               | 86.8     |

| 1.0          |                             | 1.319               | 75.7     | 1.0                  |                      | 1.368               | 72.9     |

| 0.7          |                             | 0.945               | 74.0     | 0.7                  |                      | 0.992               | 70.5     |

| 0.5          |                             | 0.690               | 72.4     | 0.5                  |                      | 0.737               | 67.6     |

Average efficiency (25, 50, 75, 100% of P<sub>out,max</sub>): **89.5%** Average efficiency (25, 50, 75, 100% of P<sub>out,max</sub>): **89.1%**

#### □ No load consumption

| on:             | 115 Vrms                             | 230 Vrms                              |  |

|-----------------|--------------------------------------|---------------------------------------|--|

| $P_{out} = 0 W$ | <i>P<sub>in</sub></i> = <b>62</b> mW | <i>P<sub>in</sub></i> = <b>107</b> mW |  |

# Conclusion

- The valley lockout technique allows to solve the valley jumping problem in QR power supplies.

- NCP1380, NCP1379 features:

- QR current-mode with valley lockout for noise immunity for high load.

- VCO mode in light load for improved efficiency.

- OPP, OVP, BO, OTP, soft-start for building safe power supplies

- A complete design method has been presented.

- It is possible to achieve standby power consumption below 100 mW at 230 Vrms with the NCP1380.

- Good efficiency at light load with Sync. Rect if the bias of the TL431 and the Sync. Rec. controller is removed.

- Mathcad spreadsheet and simulations models available.

# **For More Information**

- View the extensive portfolio of power management products from ON Semiconductor at <u>www.onsemi.com</u>

- View reference designs, design notes, and other material supporting the design of highly efficient power supplies at <u>www.onsemi.com/powersupplies</u>