# AXM0F343 MCU Programming Manual

# UM70012/D

## **Device Overview**

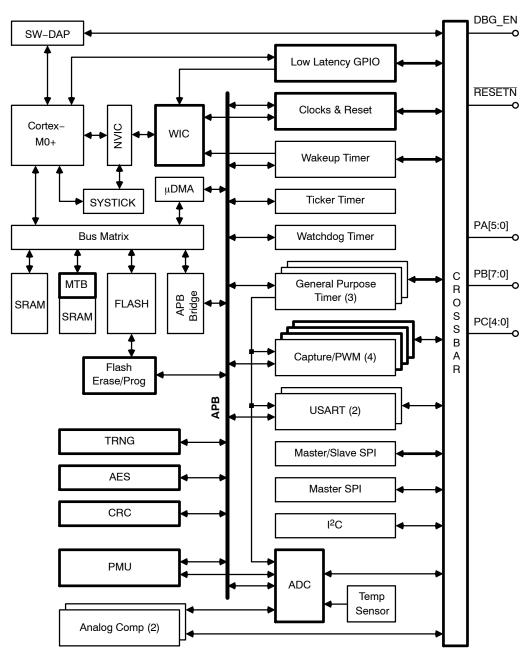

The AXM0F343 System-on-Chip (SoC) family is available with AXM0F343-64 or AXM0F343-256 ultra-low power Micro Controller Units optimized for short range radio application. AXM0F343-64 MCU and AXM0F343-256 MCU integrate the powerful and energy efficient Arm<sup>®</sup> Cortex<sup>®</sup>-M0+ microprocessor, Program Flash memory, Embedded RAM, a DMA controller, and 19 GPIO. Peripherals include: USART, SPI, I<sup>2</sup>C, timers, Capture/PWM, 12-bit 1M sample/s ADC, and analog comparators. Security features include AES and CRC acceleration engines and a true random number generator. AXM0F343 implements advanced low-power modes for ultra-low power consumption.

## Features

Arm Cortex-M0+

- ARMv6-M Architecture

- Thumb<sup>®</sup>/Thumb-2 subset instruction set

- 2 stage pipeline

- Nested Vectored Interrupt Controller (NVIC) includes 15 built–in Arm core exceptions and is configured with an additional 24 interrupts

- Non–Maskable Interrupt (NMI)

- Sleep support

- Wake-up Interrupt Controller (WIC)

- SysTick timer for scheduler

- Low latency General Purpose Input/Output (GPIO)

- Single cycle 32x32 multiply

# Debugger

- Serial-Wire Debug Access Port (SW-DAP)

- Breakpoint and single stepping support

- Micro Trace Buffer (MTB)

- · Debug port lockout

## Memory

- AXM0F343-64 MCU:

- ◆ 64 kB of FLASH

- 8 kB of RAM: 2 kB and 6 kB banks with separate power and retention control

- AXM0F343-256 MCU:

- ◆ 256 kB of FLASH

- 32 kB of RAM: 8 kB and 24 kB banks with separate power and retention control

# **ON Semiconductor®**

www.onsemi.com

# **USER MANUAL**

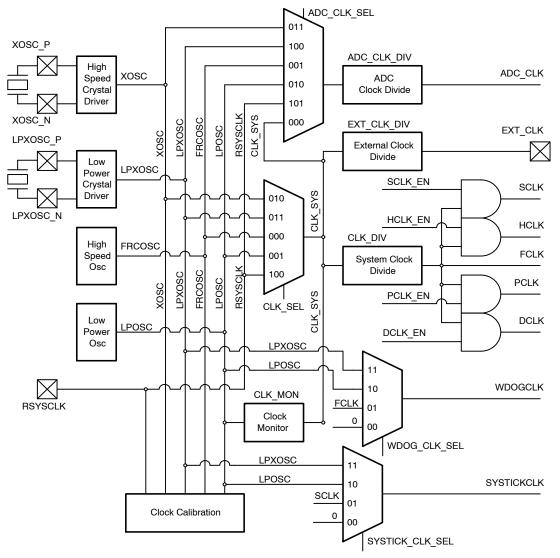

Flexible Clocking

- On-chip high speed (32/40 MHz) RC oscillator

- On-chip low power (10 kHz/640 Hz) RC oscillator

- Driver for external high speed crystal oscillator

- Driver for external low power 32.768 kHz crystal oscillator

- External clock through GPIO

- Fully automatic calibration of on-chip RC oscillators to a reference clock

- Clock monitor can detect failures of the system clock and switch to another clock

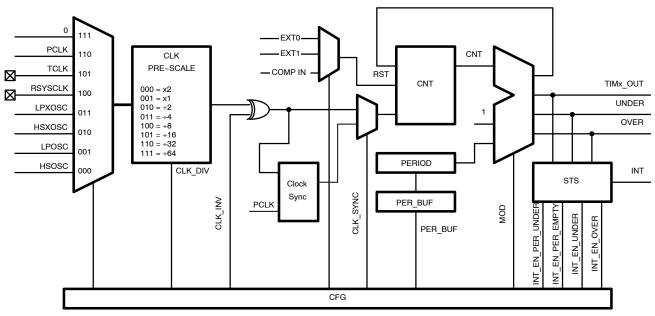

## Timers

- 32-bit wakeup timer

- 32-bit TICK timer

- General Purpose 16-bit timers (3X)

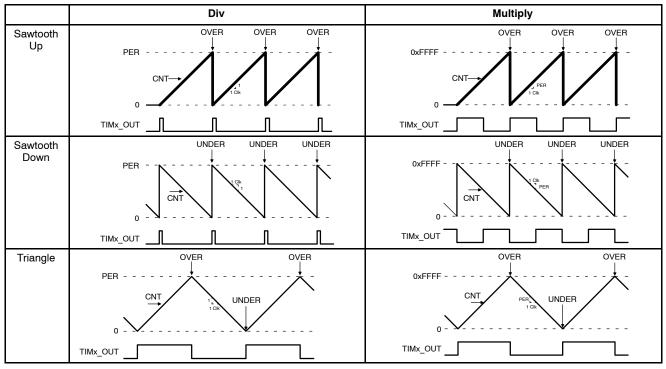

- Up count, down count (saw tooth) and up/down count (triangle) modes

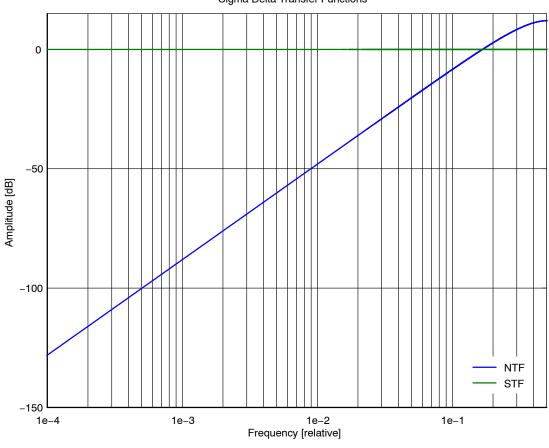

- Sigma-Delta DAC modulator mode

- Flexible clocking and pre-scale options

- Watchdog timer

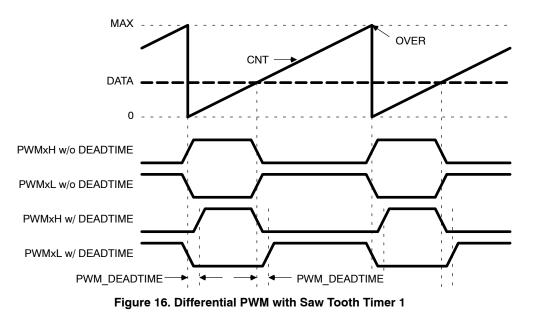

16-bit Input Capture/Output Compare/PWM Units (4X)

- Paired with any 16-bit general purpose timer

- Timer value capture at event trigger

- Compare flag at timer match

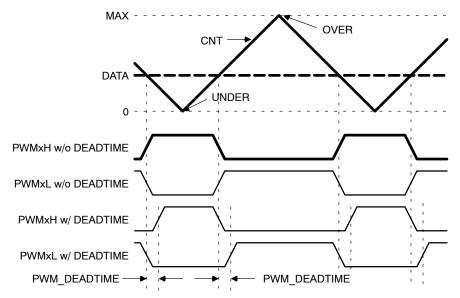

- Differential PWM with programmable dead time

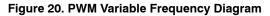

- AXM0F343 MCU TIMER/PWM

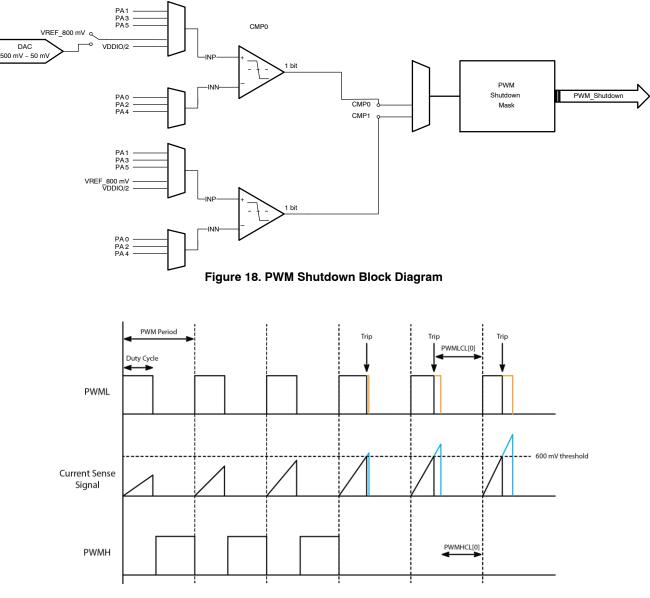

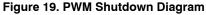

- Shutdown Operation

- Comparator DAC for Reset

- Asynchronous Reset

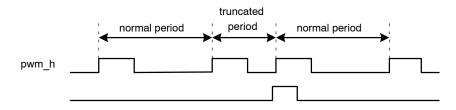

- Variable Frequency Operation

- 19 GPIO

- 6 GPIO (PA0–PA5), 8 GPIO (PB0–PB7), and 5 GPIO (PC0–PC4) can be used for both digital and analog functions

- Programmable pull-up/pull-down

- Open drain capable

- Programmable interrupts (edge/level, polarity)

# Features (continued)

• Flexible allocation of GPIO pins to peripherals through programmable crossbar

Universal Synchronous/Asynchronous Receiver/Transmitter (USART) (2x)

- 5–9 bit word length, 1–2 stop bits

- Uses any of the 16-bit general purpose timers as baud rate generator

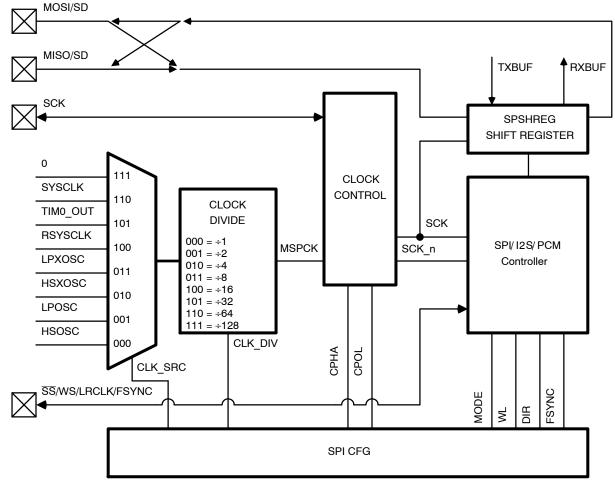

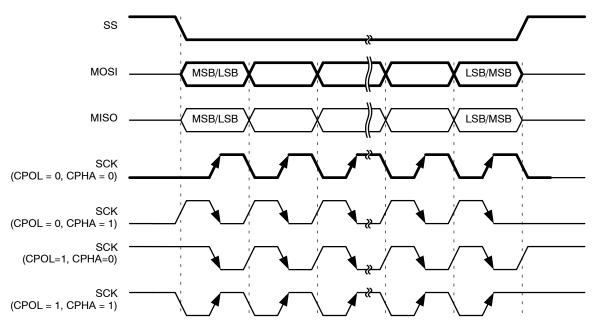

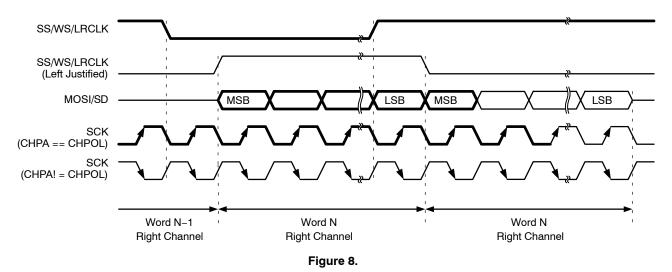

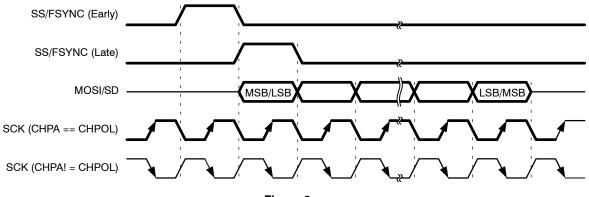

Master/Slave Serial Peripheral Interface (SPI)

- Programmable data width and direction

- Programmable phase and polarity

- Support 3-wire or 4-wire modes

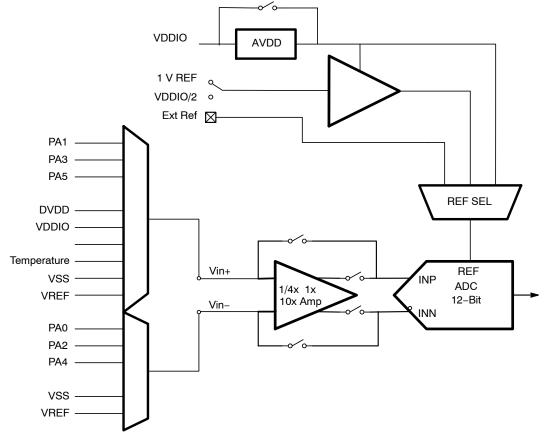

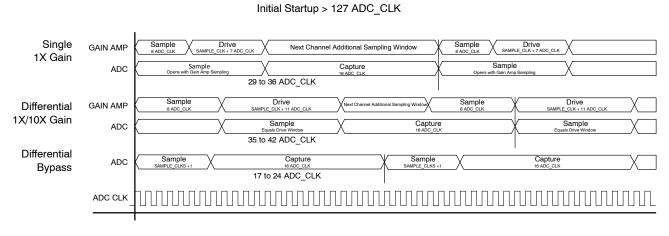

12-bit ADC

- 12-bit Max 1M samples/second

- Up to 6 external sample channels (3 differential)

- Single ended or differential sampling

- 1/4x, 1x, and 10x gain amplifier

- External or internal (1 V) reference

- Programmable conversion schedule

- Can sample internal supply and reference signals including the built-in temperature sensor

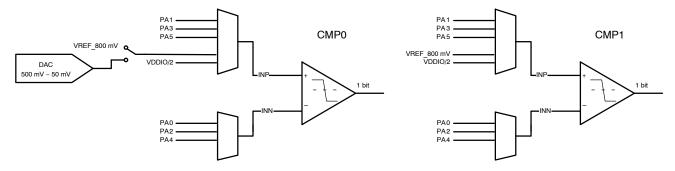

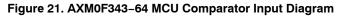

Analog Comparator (2x)

- Internal or external reference

- Output signal may be routed to GPIO, read by software, or used as input capture trigger

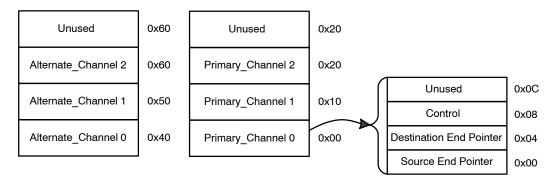

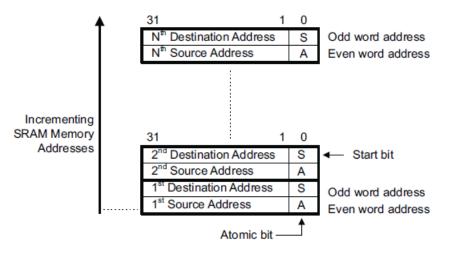

Direct Memory Access (DMA) Controller

- Arm PL230 µDMA

- 3 channels with programmable source and priority

- Supports memory-to-memory, memory-to-peripheral, and peripheral-to-memory

- Supports ping-pong, memory scatter-gather, and peripheral scatter-gather DMA cycle types

- Supports multiple transfer data widths

- 1–1024 transfers in a DMA cycle

Security Features

- Hardware Advanced Encryption Standard (AES) Acceleration

- Significant reduction in encryption/decryption time compared to software only solution

- Supports 128-bit, 192-bit, and 256-bit encryption/decryption

- Cyclic Redundancy Check (CRC) Engine

- Standard Ethernet 32-bit polynomial

- Used to verify integrity of the flash memory

- True random number generator

- Debug port lock

# **Table of Contents**

| Block Diagram                             |

|-------------------------------------------|

| Cortex-M0+ Microcontroller and Bus Fabric |

| Memory                                    |

| Power Management                          |

| Reset and Brownout                        |

| Clocks (CMU)                              |

| System Configuration                      |

| Crossbar (XBAR)                           |

| Direct Memory Access (DMA)                |

| External Communication Interfaces         |

| Timers                                    |

| Security Functions                        |

| Analog Functions                          |

| Debug Functions                           |

| Debug Functions                           |

Figure 1. Block Diagram

# ACRONYMS

# Table 1. ACRONYMS

| Acronym | Description                                             |  |  |  |

|---------|---------------------------------------------------------|--|--|--|

| ADC     | Analog to Digital Converter                             |  |  |  |

| AES     | Advanced Encryption Standard                            |  |  |  |

| AHB     | Advanced High Performance Bus                           |  |  |  |

| AMBA    | Advanced Microcontroller Bus Architecture               |  |  |  |

| APB     | Advanced Peripheral Bus                                 |  |  |  |

| CCPWM   | Compare/Capture/Pulse Width Modulation                  |  |  |  |

| CMP     | Comparator                                              |  |  |  |

| CMU     | Clock Monitor Unit                                      |  |  |  |

| CRC     | Cyclic Redundancy Check                                 |  |  |  |

| DAC     | Digital to Analog Converter                             |  |  |  |

| DAP     | Debug Access Port                                       |  |  |  |

| DMA     | Direct Memory Access Controller                         |  |  |  |

| GPIO    | General Purpose Input Output                            |  |  |  |

| I2C     | Inter-Integrated Circuit Controller                     |  |  |  |

| MCU     | Micro Controller Unit                                   |  |  |  |

| MTB     | Micro Trace Buffer                                      |  |  |  |

| NMI     | Non-Maskable Interrupt                                  |  |  |  |

| NVIC    | Nested Vectored Interrupt Controller                    |  |  |  |

| NVM     | Non Volatile Memory                                     |  |  |  |

| PMU     | Power Management Unit                                   |  |  |  |

| PWM     | Pulse Width Modulation                                  |  |  |  |

| SPI     | Serial Peripheral Interface                             |  |  |  |

| SWD     | Serial Wire Debug                                       |  |  |  |

| SW-DAP  | Serial-Wire Debug Access Port                           |  |  |  |

| TRNG    | True Random Number Generator                            |  |  |  |

| USART   | Universal Synchronous Asynchronous Receiver Transmitter |  |  |  |

| WDOG    | Watchdog timer                                          |  |  |  |

| WIC     | Wake-up Interrupt Controller                            |  |  |  |

| WUT     | Wake Up Timer                                           |  |  |  |

| XBAR    | Crossbar                                                |  |  |  |

#### Cortex-M0+ MICROCONTROLLER AND BUS FABRIC

AXM0F343 MCU integrates the powerful and energy efficient Arm Cortex–M0+ processor that includes the integrated Nested Vectored Interrupt Controller (NVIC), Wake–up Interrupt Controller(WIC), and Debug Access Port (DAP). The processor uses the Thumb instruction set and is optimized for high performance with reduced code size and low power operation. The Arm Cortex–M0+ efficiently handles multiple parallel peripherals and has integrated sleep modes. With industry standard tool chain and support, developing applications on the AXM0F343 platform reduces time to market. Test and debug capability is enhanced with the Arm Serial Wire Debug Port and Micro Trace Buffer. The microprocessor uses little–endian formatting.

The microprocessor, debug port, and memories are interconnected using the Advanced Microcontroller Bus Architecture (AMBA). A bridge is included to connect the peripherals.

Next to the regular Arm Cortex-M0+ processor interrupts, the AXM0F343 MCU implements multiple external source interrupts for peripheral devices. A powerful nested, pre-emptive and priority based interrupt handling timely and flexible response to external events.

Low power features on AXM0F343 MCU include the WIC, adjustable clock rates, and different software controlled power modes to maximize opportunities to save power in application.

#### Serial Wire Debug Access Port (SW-DAP)

The Debug Access Port is included in the Arm Cortex-M0+ implementation. The basic debug functionality includes processor halts, single-step, processor core register access, Reset and HardFault Vector Catch, unlimited software breakpoints, and full system memory access. The debug mode implementation also includes 4 hardware breakpoints and 2 hardware watch points. The Debug Port is disabled at power-up if the part is locked, and may be enabled by firmware using the Lock Override Register. Driving the debug enable pin high will prevent the part from entering a low power mode (see the PMU description).

The Debug Access Port interface implementation is the Arm Serial Wire Debug Port (SW–DP) connected to pins SWCLK and SWDIO. SWO is not implemented. The Serial Wire Debug Port Interface uses a single bi–directional data connection. Each operation consists of three phases: Packet request, Acknowledge response, and Data transfer phase. Use any Serial Wire Debug (SWD) compliant hardware debugger interface to interact with the internals of the AXM0F343 MCU.

Idle and reset: Between transfers, the host must either drive the line LOW to the IDLE state, or continue immediately with the start bit of a new transfer. The host is also free to leave the line HIGH, either driven or tri-stated, after a packet. This reduces the static current drain, but if this approach is used with a free running clock, a minimum of 50 clock cycles must be used, followed by a READ-ID as a new re-connection sequence. There is no explicit reset signal for the protocol. A reset is detected by either host or target when the expected protocol is not observed. It is important that both ends of the link become reset before the protocol can be restarted with a reconnection sequence. Re-synchronization following the detection of protocol errors or after reset is achieved by providing 50 clock cycles with the line HIGH, or tristate, followed by a read ID request. If the SW-DP detects that it has lost synchronization, for example if no stop bit is seen when expected, it leaves the line un-driven and waits for the host to either re-try with a new header after a minimum of one cycle with the line LOW, or signals a reset by not driving the line itself. If the SW-DP detects two bad data sequences in a row, it locks out until a reset sequence of 50 clock cycles with DBGDI HIGH is seen. If the host does not see an expected response from SW-DP, it must allow time for SW-DP to return a data payload. The host can then retry with a read to the SW-DP ID code register. If this is unsuccessful, the host must attempt a reset.

#### Nested Vectored Interrupt Controller (NVIC)

The Cortex–M0+ Nested Vectored Interrupt Controller (NVIC) supports priority based nested vectored interrupts. It includes 15 built–in or reserved exceptions and is configured with an additional 22 interrupts. Most interrupts have programmable priority. Priority levels available in the NVIC are 0, 64, 128, and 192. Lower numbers are higher priority. The priority of each group can be set separately by the firmware. While an interrupt is being serviced, only interrupts from a higher priority arrive at the same time, the earlier one (according to polling order) will be serviced first. The optional Wake–up Interrupt Controller (WIC) is included for low power mode support. Only a subset of the interrupts are included in the wake–up controller.

## Table 2. EXCEPTIONS AND INTERRUPTS TABLE

| Interrupt                                                             | Exception<br>Number | Priority     | Available in<br>Sleep | Available in<br>Hibernate | Available in<br>Shutdown |

|-----------------------------------------------------------------------|---------------------|--------------|-----------------------|---------------------------|--------------------------|

| Cortex M0+ - Reset                                                    | 1                   | –3 (Highest) | Yes                   | No                        | No                       |

| Cortex M0+ - NMI (external pin, clock loss, or brownout)              | 2                   | -2           | Yes                   | Yes                       | No                       |

| Cortex M0+ - Hard Fault                                               | 3                   | -1           | No                    | No                        | No                       |

| Cortex M0+ Reserved                                                   | 4–10                | N/A          | N/A                   | N/A                       | N/A                      |

| Cortex M0+ SVC                                                        | 11                  | Programmable | No                    | No                        | No                       |

| Cortex M0+ Reserved                                                   | 12–13               | N/A          | N/A                   | N/A                       | N/A                      |

| Cortex M0+ PendSV                                                     | 14                  | Programmable | No                    | No                        | No                       |

| Cortex M0+ SysTick                                                    | 15                  | Programmable | No                    | No                        | No                       |

| General Purpose I/O (GPIO)                                            | 16                  | Programmable | Yes                   | Yes                       | PB3                      |

| Wakeup Timer (WUT)                                                    | 17                  | Programmable | Yes                   | Yes                       | No                       |

| Tick Timer (TICK)                                                     | 18                  | Programmable | Yes                   | No                        | No                       |

| External Pin                                                          | 19                  | Programmable | Yes                   | Yes                       | No                       |

| Analog Comparator (CMP)                                               | 20                  | Programmable | Yes                   | No                        | No                       |

| Analog to Digital Convertor (ADC)                                     | 21                  | Programmable | Yes                   | No                        | No                       |

| True Random Number Generator (TRNG)                                   | 22                  | Programmable | Yes                   | No                        | No                       |

| FLASH                                                                 | 23                  | Programmable | No                    | No                        | No                       |

| Watchdog (WDOG)                                                       | 24                  | Programmable | No                    | No                        | No                       |

| Clock/System Config (CMU)                                             | 25                  | Programmable | Yes                   | No                        | No                       |

| Timer0 (TIM0)                                                         | 26                  | Programmable | Yes                   | No                        | No                       |

| Timer1 (TIM1)                                                         | 27                  | Programmable | Yes                   | No                        | No                       |

| Timer2 (TIM2)                                                         | 28                  | Programmable | Yes                   | No                        | No                       |

| Capture/PWM 0 (CPMW0)                                                 | 29                  | Programmable | Yes                   | No                        | No                       |

| Capture/PWM 1 (CPMW1)                                                 | 30                  | Programmable | Yes                   | No                        | No                       |

| Capture/PWM 2 (CPMW2)                                                 | 31                  | Programmable | Yes                   | No                        | No                       |

| Capture/PWM 3 (CPMW3)                                                 | 32                  | Programmable | Yes                   | No                        | No                       |

| Reserved                                                              | 33                  | N/A          | N/A                   | N/A                       | N/A                      |

| Master/Slave SPI (SPI)                                                | 34                  | Programmable | Yes                   | No                        | No                       |

| Universal Synchronous/Asynchronous<br>Receiver/Transmitter 0 (USART0) | 35                  | Programmable | Yes                   | No                        | No                       |

| Universal Synchronous/Asynchronous<br>Receiver/Transmitter 1 (USART1) | 36                  | Programmable | Yes                   | No                        | No                       |

| I <sup>2</sup> C (I2C)                                                | 37                  | Programmable | Yes                   | No                        | No                       |

| DMA_ERROR                                                             | 38                  | Programmable | Yes                   | No                        | No                       |

| DMA_DONE                                                              | 39                  | Programmable | Yes                   | No                        | No                       |

## AHB-APB Bridge with Atomic RMW

The APB peripheral bus is connected to the AHB bus using a bridge that includes support for Atomic Read-Modify-Write (RMW) capability. APB peripheral reads ignore the Atomic RMW bits, reading the target register contents normally for all settings.

Address bits [27:26] are used to configure an APB write as one of four modes:

| Table 3. |  |

|----------|--|

|----------|--|

| Address [27:26] | Write Operation                                                                                                                                                          |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 00              | Direct Write – a normal write operation which transfers the write data directly into the targeted peripheral register overwriting the previous contents.                 |

| 01              | Clear or AND'ed Write – used for bit clearing as it first AND's the contents of the target register with the write data and places the result in the target register.    |

| 10              | Set or OR'ed Write – used for bit setting as it first OR's the contents of the target register with the write data and places the result in the target register.         |

| 11              | Inverted or XOR'ed Write – used for bit toggling as it first XOR's the contents of the target register with the write data and places the result in the target register. |

Usage of the atomic read-modify-write capability can facilitated through macros:

```

#define ATOMIC_CLEAR(x) *((volatile uint32_t *) ((uint32_t) (&(x)) + (1<<26))

#define ATOMIC_SET(x) *((volatile uint32_t *) ((uint32_t) (&(x)) + (2<<26))

#define ATOMIC_TOGGLE(x) *((volatile uint32_t *) ((uint32_t) (&(x)) + (3<<26))</pre>

```

Or alternatively using #define aliases for each peripheral:

| #define AND_OFFSET | 0x0400000UL                             |

|--------------------|-----------------------------------------|

| #define OR_OFFSET  | 0x0800000UL                             |

| #define XOR_OFFSET | 0x0C0000UL                              |

| #define GPIO_AND   | ((GPIO_Type*) (GPIO_BASE + AND_OFFSET)) |

| #define GPIO_OR    | ((GPIO_Type*) (GPIO_BASE + OR_OFFSET))  |

| #define GPIO_XOR   | ((GPIO_Type*) (GPIO_BASE + XOR_OFFSET)) |

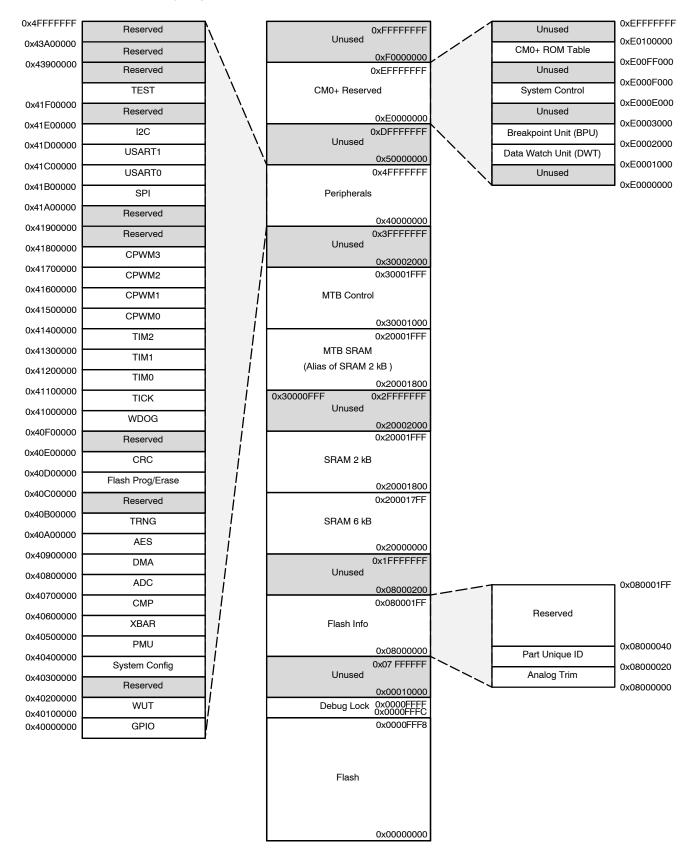

## MEMORY

The 32-bit memory address space is broken up into regions for code, data, and multi-use. Memory elements consist of registers, SRAM, and Non-Volatile Memory Flash (NVM Flash). A memory region is dedicated to the IOP and APB peripheral access. There are also built in regions for built in Arm registers and peripherals. There are many unused portions of the memory space. Attempted access to these unused regions will result in a memory fault. Individual memory regions and elements are described in the next few sections.

The AXM0F343 MCU is available in two different memory configurations:

- AXM0F343-64 which contains 64 kB of FLASH and 8 kB of RAM

- AXM0F343–256 which contains 256 kB of FLASH and 32 kB of RAM

### AXM0F343-64 MCU Memory Map

Figure 2. AXM0F343-64 MCU Memory Map

## AXM0F343 MCU Memory Map

| 045555555  |                  |              |                   |                          |      |                       |              |

|------------|------------------|--------------|-------------------|--------------------------|------|-----------------------|--------------|

| 0x4FFFFFFF | Reserved         | N I          |                   | 0xFFFFFFFF               | ] _/ | Unused                | 0xEFFFFFFF   |

| 0x43A00000 | Reserved         | $\backslash$ | Unused            | 0xF0000000               |      | CM0+ ROM Table        | 0xE1000000   |

| 0x43900000 | Reserved         | Ň            |                   | 0xF0000000               | r i  | Unused                | 0xE00FF000   |

| 0x41E00000 | I2C              |              | CM0+ Reserv       | ved                      | -    | System Control        | 0xE000F000   |

| 0x41D00000 | USART1           | Ň            |                   |                          |      | Unused                | 0xE000E000   |

| 0x41C00000 | USARTO           | N N          |                   | 0xE0000000<br>0xDFFFFFFF | k +  |                       | 0xE0003000   |

| 0x41B00000 |                  |              | Unused            |                          |      | Breakpoint Unit (BPU) | 0xE0002000   |

| 0x41A00000 | Master/Slave SPI | Ň            |                   | 0x50000000<br>0x4FFFFFF  |      | Data Watch Unit (DWT) | 0xE0001000   |

| 0x41900000 | Reserved         |              |                   | UX4FFFFFFF               |      | Unused                | 0xE0000000   |

| 0x41800000 | Reserved         |              | Peripherals       |                          |      |                       |              |

| 0x41700000 | CCPWM3           |              |                   | 0x40000000               |      |                       |              |

| 0x41600000 | CCPWM2           |              | Unused            | 0x3FFFFFFF               |      |                       |              |

|            | CCPWM1           |              |                   | 0x30004000               |      |                       |              |

| 0x41500000 | CCPWM0           | i            | Coresight™ ROM    | 0x30003FFF               | 1    |                       |              |

| 0x41400000 | GP Timer2        |              | <b>.</b>          | 0x30003000               |      |                       |              |

| 0x41300000 | GP Timer1        |              | MTB Control       | 0,20002000               |      |                       |              |

| 0x41200000 | GP Timer0        | į            |                   | 0x30002000<br>0x20001FFF |      |                       |              |

| 0x41100000 | Ticker Timer     |              | MTB SRAM          |                          |      |                       |              |

| 0x41000000 | Watchdog         | i            | (Alias of SRAM_A) |                          |      |                       |              |

| 0x40F00000 | Reserved         | !            |                   | 0x20000000<br>0x30001FFF |      |                       |              |

| 0x40E00000 | CRC              |              | Unused            |                          |      |                       |              |

| 0x40D00000 | Flash Prog/Erase | į            |                   | 0x20008000<br>0x20007FFF |      |                       |              |

| 0x40C00000 | _                |              | SRAM_D (8 kB)     | 0x20006000               |      |                       |              |

| 0x40B00000 | Reserved         | i            | SRAM_C (8 kB)     | 0x20005FFF               |      |                       |              |

| 0x40A00000 | TRNG             | !            |                   | 0x20004000               |      |                       |              |

| 0x40900000 | AES              |              | SRAM_B (8 kB)     | 0x20003FFF               |      |                       |              |

| 0x40800000 | DMA              | i            |                   | 0x20002000<br>0x20001FFF |      |                       |              |

|            | ADC              |              | SRAM_A (8 kB)     | 0x20000000               |      |                       |              |

| 0x40700000 | Analog Comp      |              | Unused            | 0x1FFFFFFF               |      |                       |              |

| 0x40600000 | XBAR             | ļ            | Ollused           | 0x00200800               |      |                       | 0x002001FF   |

| 0x40500000 | PMU              |              |                   | 0x002001FF               |      | D.                    |              |

| 0x40400000 | System Config    | i            | Flash Info        |                          |      | Reserved              |              |

| 0x40300000 | Reserved         | !            |                   | 0,00000000               |      |                       | 0x00200040   |

| 0x40200000 | Wakeup Timer     | 1            |                   | 0x00200000<br>0x001FFFFF |      | Part Unique ID        | 0x00200020   |

| 0x40100000 | GPIO             | į            | Unused            |                          |      | Analog Trim           | 0x00200000   |

| 0x40000000 |                  |              |                   | 0x00040000<br>0x0003FFFF |      |                       | - 0x00200000 |

|            |                  |              | Debug Lock        | 0x0003FFFC               |      |                       |              |

|            |                  |              |                   | 0x0003FFF8               |      |                       |              |

|            |                  |              |                   |                          |      |                       |              |

|            |                  |              | Flash             |                          |      |                       |              |

|            |                  |              |                   |                          |      |                       |              |

|            |                  |              |                   |                          |      |                       |              |

|            |                  |              |                   | 0x00000000               |      |                       |              |

|            |                  |              |                   |                          |      |                       |              |

Figure 3. AXM0F343-256 MCU Memory Map

# Peripheral Memory Address Decode

The APB and IOP peripherals are accessed in the address range of 0x40000000 to 0x4FFF\_FFFF. Within this range peripheral addresses are decoded as such.

## Table 4.

| Bit Range | Purpose                                                                                                                          |  |  |  |  |  |

|-----------|----------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| [31:28]   | Must be 0x4 to access peripheral space.                                                                                          |  |  |  |  |  |

| [27:26]   | Atomic read-modify-write operation. Ignored for reads.<br>00 – Direct write, 01 – Clear write, 10 – Set write, 11 – Toggle write |  |  |  |  |  |

| [25]      | Generally this bit is ignored and will alias if used.                                                                            |  |  |  |  |  |

| [24:20]   | Peripheral select decode.                                                                                                        |  |  |  |  |  |

| [19:12]   | Generally these bits are ignored and will alias if used.                                                                         |  |  |  |  |  |

| [11:2]    | Available for register offset within peripheral.                                                                                 |  |  |  |  |  |

| [1:0]     | Byte select within peripheral register. Most, but not all peripherals support byte and half-word accesses.                       |  |  |  |  |  |

### Peripheral Register Table Summary

#### Table 5. PERIPHERAL REGISTER TABLE SUMMARY

| GPIO           DATA         0x4000000           DATA_OUT         0x4000004           OUT_EN         0x4000008           INT_EN         0x4000000C           INT_POL         0x40000010           INT_TYP         0x40000014           DMA_TRIG_EN         0x40000018           INT_STS         0x4000001C           WAKEUP TIMER (WUT)         CFG | RO<br>R/W<br>R/W<br>R/W<br>R/W | Current GPIO value for read<br>Value to apply to GPIO outputs<br>Output enable for GPIO<br>GPIO interrupt enable<br>GPIO interrupt polarity |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| DATA_OUT         0x40000004           OUT_EN         0x40000008           INT_EN         0x4000000C           INT_POL         0x40000010           INT_TYP         0x40000014           DMA_TRIG_EN         0x4000001C           INT_STS         0x4000001C           WAKEUP TIMER (WUT)         CFG                                               | R/W<br>R/W<br>R/W<br>R/W       | Value to apply to GPIO outputs<br>Output enable for GPIO<br>GPIO interrupt enable                                                           |

| OUT_EN         0x4000008           INT_EN         0x400000C           INT_POL         0x40000010           INT_TYP         0x40000014           DMA_TRIG_EN         0x40000018           INT_STS         0x4000001C           WAKEUP TIMER (WUT)         CFG                                                                                       | R/W<br>R/W<br>R/W              | Output enable for GPIO<br>GPIO interrupt enable                                                                                             |

| INT_EN         0x400000C           INT_POL         0x40000010           INT_TYP         0x40000014           DMA_TRIG_EN         0x40000018           INT_STS         0x4000001C           WAKEUP TIMER (WUT)         CFG                                                                                                                          | R/W<br>R/W                     | GPIO interrupt enable                                                                                                                       |

| INT_POL         0x40000010           INT_TYP         0x40000014           DMA_TRIG_EN         0x40000018           INT_STS         0x4000001C           WAKEUP TIMER (WUT)         CFG                                                                                                                                                             | R/W                            |                                                                                                                                             |

| INT_TYP         0x40000014           DMA_TRIG_EN         0x40000018           INT_STS         0x4000001C           WAKEUP TIMER (WUT)         CFG                                                                                                                                                                                                  |                                | GPIO interrunt polarity                                                                                                                     |

| DMA_TRIG_EN         0x40000018           INT_STS         0x4000001C           WAKEUP TIMER (WUT)         CFG         0x40100000                                                                                                                                                                                                                    | R/W                            | or to interrupt polarity                                                                                                                    |

| INT_STS         0x4000001C           WAKEUP TIMER (WUT)         CFG         0x40100000                                                                                                                                                                                                                                                             |                                | GPIO interrupt type                                                                                                                         |

| WAKEUP TIMER (WUT) CFG 0x40100000                                                                                                                                                                                                                                                                                                                  | R/W                            | GPIO DMA enable                                                                                                                             |

| CFG 0x40100000                                                                                                                                                                                                                                                                                                                                     | R/W                            | GPIO interrupt status                                                                                                                       |

|                                                                                                                                                                                                                                                                                                                                                    |                                |                                                                                                                                             |

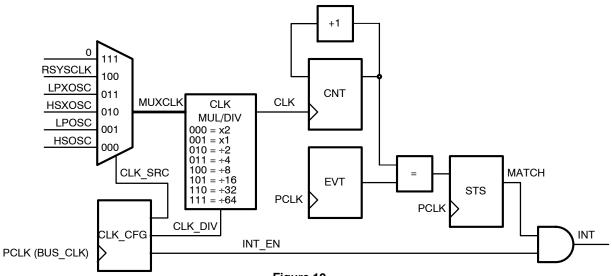

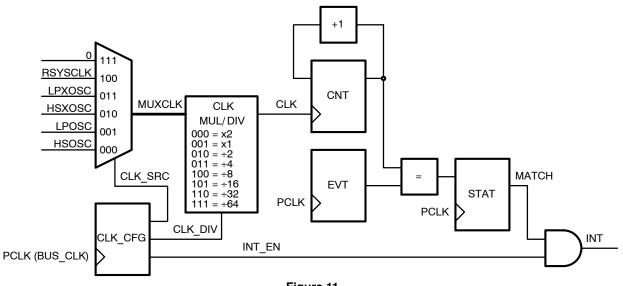

|                                                                                                                                                                                                                                                                                                                                                    | R/W                            | Wakeup timer configuration including clock source and pre-scale                                                                             |

| STS 0x40100004                                                                                                                                                                                                                                                                                                                                     | RO                             | Wakeup timer status register                                                                                                                |

| CNT 0x40100008                                                                                                                                                                                                                                                                                                                                     | RO                             | Wakeup timer value                                                                                                                          |

| EVT 0x4010000C                                                                                                                                                                                                                                                                                                                                     | R/W                            | Wakeup timer event matching value                                                                                                           |

| CLOCK AND SYSTEM CONFIGURATION (CMU)                                                                                                                                                                                                                                                                                                               |                                |                                                                                                                                             |

| CFG 0x40300000                                                                                                                                                                                                                                                                                                                                     | R/W                            | System clock configuration                                                                                                                  |

| STS 0x40300004                                                                                                                                                                                                                                                                                                                                     | RO                             | Clock status                                                                                                                                |

| ADCCLK_CFG 0x40300008                                                                                                                                                                                                                                                                                                                              | R/W                            | ADC clock source and pre-scale                                                                                                              |

| EXTCLK_CFG 0x4030000C                                                                                                                                                                                                                                                                                                                              | R/W                            | External clock source select and clock divide                                                                                               |

| PCLK_EN 0x40300010                                                                                                                                                                                                                                                                                                                                 | R/W                            | Enables the individual peripheral clocks                                                                                                    |

| LPOSC_CFG 0x40300014                                                                                                                                                                                                                                                                                                                               | R/W                            | Low power RC oscillator configuration                                                                                                       |

| LPOSC_FILT 0x40300018                                                                                                                                                                                                                                                                                                                              | R/W                            | Low power RC oscillator calibration filter                                                                                                  |

| LPOSC_REF_DIV 0x4030001C                                                                                                                                                                                                                                                                                                                           | R/W                            | Low power RC oscillator calibration reference divide                                                                                        |

| LPOSC_TRIM 0x40300020                                                                                                                                                                                                                                                                                                                              | R/W                            | Low power RC oscillator calibration frequency tune value                                                                                    |

| LPOSC_PER 0x40300024                                                                                                                                                                                                                                                                                                                               | RO                             | Low power RC oscillator calibration measured value                                                                                          |

| HSOSC_CFG 0x40300028                                                                                                                                                                                                                                                                                                                               |                                |                                                                                                                                             |

| Peripheral Register     | Address       | Access | Description                                                       |

|-------------------------|---------------|--------|-------------------------------------------------------------------|

| CLOCK AND SYSTEM CONFIG | URATION (CMU) |        |                                                                   |

| HSOSC_FILT              | 0x4030002C    | R/W    | High speed RC oscillator calibration filter                       |

| HSOSC_REF_DIV           | 0x40300030    | R/W    | High speed RC oscillator calibration reference divide             |

| HSOSC_40M_FREQ_TUNE     | 0x40300034    | R/W    | High speed RC oscillator 40MHz calibration frequency tune value   |

| HSOSC_32M_FREQ_TUNE     | 0x40300038    | R/W    | High speed RC oscillator 32MHz calibration frequency tune value   |

| HSOSC_PER               | 0x4030003C    | RO     | High speed RC oscillator calibration measured value               |

| RESERVED                | 0x40300040    | -      |                                                                   |

| OSC_READY_STS           | 0x40300044    | RO     | Indicates if clock sources are enabled and stable                 |

| INT_STS                 | 0x40300048    | R/W    | Clock interrupt enables                                           |

| LPXOSC_GM_CFG           | 0x4030004C    | R/W    | Low power crystal oscillator transconductance configuration       |

| RESERVED                | 0x40300050    | -      |                                                                   |

| HSXOSC_GM_CFG           | 0x40300054    | R/W    | High speed crystal oscillator transconductance configuration      |

| HSXOSC_AMPL_CFG         | 0x40300058    | R/W    | Controls the crystal transconductance servo loop                  |

| HSXOSC_READY            | 0x4030005C    | R/W    | Crystal oscillator ready mode and status                          |

| AO_SCRATCH              | 0x40300060    | R/W    | Always on scratch register for retention in ultra-low power modes |

| INT_LAT                 | 0x40300064    | R/W    | Controls the latency controls for interrupts                      |

| POWER MANAGEMENT UNIT ( | (PMU)         |        |                                                                   |

| POWER_MODE              | 0x40400000    | R/W    | Controls power mode options                                       |

| POWER_DOWN              | 0x40400004    | R/W    | Powers down the SRAM banks                                        |

| STS                     | 0x40400008    | RO     | Power mode status                                                 |

| CROSSBAR (XBAR)         |               |        |                                                                   |

| ANA_EN                  | 0X40500000    | R/W    | PA0-PA5 analog function enable                                    |

| DRIVE_TYPE              | 0X40500004    | R/W    | Pin drive type configuration                                      |

| PULL_UP                 | 0X40500008    | R/W    | Pin pullup enables                                                |

| PULL_DOWN               | 0X4050000C    | R/W    | Pin pulldown enables                                              |

| PA_CFG                  | 0X40500010    | R/W    | Bank A output pin function configuration                          |

| PB_CFG                  | 0X40500014    | R/W    | Bank B output pin function configuration                          |

| PC_CFG                  | 0X40500018    | R/W    | Bank C output pin function configuration                          |

| RESERVED                | 0X4050001C    | -      |                                                                   |

| IN_USART0_CFG           | 0X40500020    | R/W    | USART0 input pin configuration                                    |

| IN_USART1_CFG           | 0X40500024    | R/W    | USART1 input pin configuration                                    |

| IN_SPI_CFG              | 0X40500028    | R/W    | Master/Slave SPI input pin configuration                          |

| RESERVED                | 0X4050002C    | -      |                                                                   |

| IN_DMA_CFG              | 0X40500030    | R/W    | DMA trigger source configuration                                  |

| IN_ADC_CFG              | 0X40500034    | R/W    | ADC trigger source configuration                                  |

| IN_TIM0_CFG             | 0X40500038    | R/W    | Timer0 source clock configuration                                 |

| IN_TIM1_CFG             | 0X4050003C    | R/W    | Timer1 source clock configuration                                 |

| IN_TIM2_CFG             | 0X40500040    | R/W    | Timer2 source clock configuration                                 |

| IN_CAPT0_CFG            | 0X40500044    | R/W    | Capture0 source trigger configuration                             |

| IN_CAPT1_CFG            | 0X40500048    | R/W    | Capture1 source trigger configuration                             |

| IN_CAPT2_CFG            | 0X4050004C    | R/W    | Capture2 source trigger configuration                             |

| IN_CAPT3_CFG            | 0X40500050    | R/W    | Capture3 source trigger configuration                             |

| Peripheral Register       | Address        | Access | Description                                                           |  |  |

|---------------------------|----------------|--------|-----------------------------------------------------------------------|--|--|

| CROSSBAR (XBAR)           |                | •      | •                                                                     |  |  |

| IN_EXTCLK_CFG             | 0X40500054     | R/W    | External source clock configuration                                   |  |  |

| <test reserved=""></test> | 0X40500058     | R/W    | Don't use                                                             |  |  |

| IN_MTB_CFG                | 0X4050005C     | R/W    | MTB (TSTART/TSTOP) source configuration                               |  |  |

| EXT_INT_SEL               | 0X40500060     | R/W    | Connects external interrupt source and set polarity                   |  |  |

| EXT_INT_EN                | 0X40500064     | R/W    | Enables interrupt generation from the selected external interrupt pin |  |  |

| EXT_INT_STS               | 0X40500068     | R/W    | Shows the interrupt status selected in EXT_IN_SEL                     |  |  |

| NMI_CFG                   | 0X4050006C     | R/W    | Configure External Non-Maskable Interrupt                             |  |  |

| BRO_STS                   | 0X40500070     | R/W    | Shows the Brownout status                                             |  |  |

| PWM_EXT_IN                | 0X40500074     | R/W    | AXM0F343-64 MCU Timer or PWM Shutdown reset external pin              |  |  |

| ANALOG COMPARATOR (CM     | IP)            | •      | •                                                                     |  |  |

| OUT                       | 0x40600000     | RO     | Read the output of the comparator values                              |  |  |

| CFG                       | 0x40600004     | R/W    | Analog comparator configuration                                       |  |  |

| INT_EN                    | 0x40600008     | R/W    | Analog comparator interrupt enables                                   |  |  |

| INT_STS                   | 0x4060000C     | R/W    | Analog comparator interrupt status                                    |  |  |

| ANALOG DIGITAL CONVERT    | ER (ADC)       |        |                                                                       |  |  |

| DATA                      | 0x40700000     | RO     | ADC result                                                            |  |  |

| CFG                       | 0x40700004     | R/W    | ADC configuration                                                     |  |  |

| CTL                       | 0x40700008     | R/W    | ADC trigger and mode controls                                         |  |  |

| CAL                       | 0x4070000C     | R/W    | ADC calibration trigger                                               |  |  |

| INT_EN                    | 0x40700010     | R/W    | ADC interrupt enables                                                 |  |  |

| INT_STS                   | 0x40700014     | R/W    | ADC interrupt status                                                  |  |  |

| RESERVED                  | 0x40700018     | R/W    | Don't use                                                             |  |  |

| CH_STS                    | 0x40700018     | RO     | ADC channel from last completed measurement                           |  |  |

| STS                       | 0x4070001C     | R/W    | ADC status                                                            |  |  |

| DIRECT MEMORY ACCESS O    | CONTROLLER (DM | IA)    |                                                                       |  |  |

| STS                       | 0x40800000     | RO     | DMA status                                                            |  |  |

| CFG                       | 0x40800004     | WO     | DMA configuration                                                     |  |  |

| CTL_BASE_PTR              | 0x40800008     | R/W    | Pointer to the address of the primary data structure                  |  |  |

| ALT_CTL_BASE_PTR          | 0x4080000C     | RO     | Pointer to the address of the alternative data structure              |  |  |

| WAIT_ON_REQ_STS           | 0x40800010     | RO     | DMA wait on request status                                            |  |  |

| SW_REQ                    | 0x40800014     | WO     | SW initiated DMA request trigger                                      |  |  |

| USE_BURST_SET             | 0x40800018     | R/W    | Sets the option to use bursts                                         |  |  |

| USE_BURST_CLR             | 0x4080001C     | WO     | Clears the option to use bursts                                       |  |  |

| REQ_MASK_SET              | 0x40800020     | R/W    | Sets the DMA request mask                                             |  |  |

| REQ_MAST_CLR              | 0x40800024     | WO     | Clears the DMA request mask                                           |  |  |

| EN_SET                    | 0x40800028     | R/W    | Enables the DMA channel                                               |  |  |

| EN_CLR                    | 0x4080002C     | WO     | Disables the DMA channel                                              |  |  |

| PRI_ALT_SEL_SET           | 0x40800030     | R/W    | Sets the DMA primary/alternate select                                 |  |  |

| PRI_ALT_CLR               | 0x40800034     | WO     | Clears the DMA primary/alternate select                               |  |  |

| PRIO_SET                  | 0x40800038     | R/W    | Sets the DMA channel priority register                                |  |  |

| PRIO_CLR                  | 0x4080003C     | WO     | Clears the DMA channel priority register                              |  |  |

| Peripheral Register                 | Address                               | Access | Description                                             |  |  |  |  |

|-------------------------------------|---------------------------------------|--------|---------------------------------------------------------|--|--|--|--|

| DIRECT MEMORY ACCESS CO             | DIRECT MEMORY ACCESS CONTROLLER (DMA) |        |                                                         |  |  |  |  |

| RESERVED                            | 0x40800040 -<br>0x40800048            | -      |                                                         |  |  |  |  |

| ERR_CLR                             | 0x4080004C                            | R/W    | DMA error status and clear                              |  |  |  |  |

| INT_EN                              | 0x40800050                            | R/W    | DMA interrupt enables                                   |  |  |  |  |

| INT_STS                             | 0x40800054                            | R/W    | DMA interrupt status                                    |  |  |  |  |

| DVANCED ENCRYPTION STANDARD (AES)   |                                       |        |                                                         |  |  |  |  |

| CTL                                 | 0x40900000                            | R/W    | AES operation to perform                                |  |  |  |  |

| INPUT                               | 0x40900004                            | WO     | AES data to operate on                                  |  |  |  |  |

| OUTPUT                              | 0x40900008                            | RO     | AES result                                              |  |  |  |  |

| TRUE RANDOM NUMBER GENERATOR (TRNG) |                                       |        |                                                         |  |  |  |  |

| CFG                                 | 0x40A00000                            | R/W    | Random number configuration and status                  |  |  |  |  |

| DATA                                | 0x40A00000                            | RO     | Random number result                                    |  |  |  |  |

| FLASH CONTROL (FLASH)               |                                       |        |                                                         |  |  |  |  |

| CTL                                 | 0x40C00000                            | R/W    | Flash program and erase control                         |  |  |  |  |

| ADDR                                | 0x40C00004                            | R/W    | Address to be programmed or erased                      |  |  |  |  |

| DATA                                | 0x40C00008                            | R/W    | Data to program into the flash                          |  |  |  |  |

| INT_EN                              | 0x40C0000C                            | R/W    | Flash interrupt enable                                  |  |  |  |  |

| RESERVED                            | 0x40C00010                            | R/W    | Don't use                                               |  |  |  |  |

| INT_STS                             | 0x40C00014                            | R/W    | Flash interrupt status                                  |  |  |  |  |

| PROT0                               | 0x40C00018                            | R/W    | Flash page 0-31 protection                              |  |  |  |  |

| PROT1                               | 0x40C0001C                            | R/W    | Flash page 32-63 protection                             |  |  |  |  |

| PROT2                               | 0x40C00020                            | R/W    | Flash page 64-95 protection                             |  |  |  |  |

| PROT3                               | 0x40C00024                            | R/W    | Flash page 96-127 protection                            |  |  |  |  |

| DMA_EN                              | 0x40C00028                            | R/W    | Enable DMA trigger generation on erase/program complete |  |  |  |  |

| CYCLIC REDUNDANCY CHEC              | K (CRC)                               |        |                                                         |  |  |  |  |

| RESULT                              | 0x40D00000                            | R/W    | Current CRC value                                       |  |  |  |  |

| INPUT                               | 0x40D00004                            | WO     | Data to add to the CRC                                  |  |  |  |  |

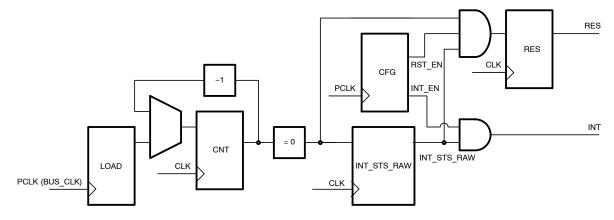

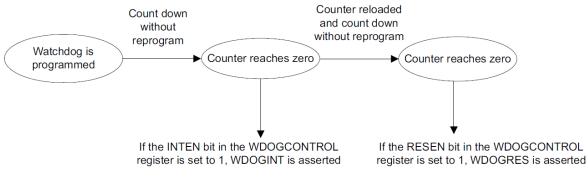

| WATCHDOG (WDOG)                     |                                       |        |                                                         |  |  |  |  |

| LOAD                                | 0x40F00000                            | R/W    | Watchdog load value                                     |  |  |  |  |

| VAL                                 | 0x40F00004                            | RO     | Current watchdog counter value                          |  |  |  |  |

| CFG                                 | 0x40F00008                            | R/W    | Watchdog configuration                                  |  |  |  |  |

| RESERVED                            | 0x40F0000C                            | _      | Don't use                                               |  |  |  |  |

| INT_STS_RAW                         | 0x40F00010                            | RO     | Watchdog raw interrupt status                           |  |  |  |  |

| INT_STS                             | 0x40F00014                            | R/W    | Watchdog interrupt status                               |  |  |  |  |

| RESERVED                            | 0x40F00018 -<br>0x40F00BFC            | -      | Don't use                                               |  |  |  |  |

| LOCK                                | 0x40F00C00                            | R/W    | Watchdog unlock                                         |  |  |  |  |

| RESERVED                            | 0x40F00C04 -<br>0x40F00EFC            | _      | Don't use                                               |  |  |  |  |

| RESERVED                            | 0x40F00F00 -<br>x40F00F04             | _      | Don't use                                               |  |  |  |  |

| Peripheral Register    | Address        | Access | Description                                                    |

|------------------------|----------------|--------|----------------------------------------------------------------|

| TICK TIMER (TICK)      |                |        | ·                                                              |

| CFG                    | 0x41000000     | R/W    | TICK timer configuration                                       |

| STS                    | 0x41000004     | RO     | TICK timer status                                              |

| CNT                    | 0x41000008     | RO     | TICK timer counter value                                       |

| EVT                    | 0x4100000C     | R/W    | TICK timer event match value                                   |

| 16-bit GENERAL PURPOSE | TIMER 0 (TIMO) |        | •                                                              |

| CNT                    | 0x41100000     | R/W    | Timer 0 count value                                            |

| PER                    | 0x41100004     | R/W    | Timer 0 rollover value, step value, or $\Sigma\Delta$ DAC code |

| CFG                    | 0x41100008     | R/W    | Timer 0 configuration                                          |

| INT_STS                | 0x4110000C     | R/W    | Timer 0 status                                                 |

| 16-bit GENERAL PURPOSE | TIMER 1 (TIM1) |        |                                                                |

| CNT                    | 0x41200000     | R/W    | Timer 1 count value                                            |

| PER                    | 0x41200004     | R/W    | Timer 1 rollover value, step value, or $\Sigma\Delta$ DAC code |

| CFG                    | 0x41200008     | R/W    | Timer 1 configuration                                          |

| INT_STS                | 0x4120000C     | R/W    | Timer 1 status                                                 |

| 16-bit GENERAL PURPOSE | TIMER 2 (TIM2) |        |                                                                |

| CNT                    | 0x41300000     | R/W    | Timer 2 count value                                            |

| PER                    | 0x41300004     | R/W    | Timer 2 rollover value, step value, or $\Sigma\Delta$ DAC code |

| CFG                    | 0x41300008     | R/W    | Timer 2 configuration                                          |

| INT_STS                | 0x4130000C     | R/W    | Timer 2 status                                                 |

| COMPARE/CAPTURE/PWM L  | JNIT 0 (CPWM0) |        |                                                                |

| CFG                    | 0x41400000     | R/W    | CPWM0 configuration                                            |

| STS                    | 0x41400004     | R/W    | CPWM0 status                                                   |

| DATA                   | 0x41400008     | R/W    | CPWM0 capture data and PWM threshold                           |

| SHUTDOWN_CFG           | 0x4140000C     | R/W    | CPWM0 Shutdown control                                         |

| COMPARE/CAPTURE/PWM L  | JNIT 1 (CPWM1) |        |                                                                |

| CFG                    | 0x41500000     | R/W    | CPWM1 configuration                                            |

| STS                    | 0x41500004     | R/W    | CPWM1 status                                                   |

| DATA                   | 0x41500008     | R/W    | CPWM1 capture data and PWM threshold                           |

| SHUTDOWN_CFG           | 0x4150000C     | R/W    | CPWM1 Shutdown control                                         |

| COMPARE/CAPTURE/PWM U  | JNIT 2 (CPWM2) |        |                                                                |

| CFG                    | 0x41600000     | R/W    | CPWM2 configuration                                            |

| STS                    | 0x41600004     | R/W    | CPWM2 status                                                   |

| DATA                   | 0x41600008     | R/W    | CPWM2 capture data and PWM threshold                           |

| SHUTDOWN_CFG           | 0x4160000C     | R/W    | CPWM2 Shutdown control                                         |

| COMPARE/CAPTURE/PWM U  | JNIT 3 (CPWM3) |        |                                                                |

| CFG                    | 0x41700000     | R/W    | CPWM3 configuration                                            |

| STS                    | 0x41700004     | R/W    | CPWM3 status                                                   |

| DATA                   | 0x41700008     | R/W    | CPWM3 capture data and PWM threshold                           |

| SHUTDOWN_CFG           | 0x4170000C     | R/W    | CPWM3 Shutdown control                                         |

|                        |                |        |                                                                |

## Table 5. PERIPHERAL REGISTER TABLE SUMMARY (continued)

| Peripheral Register    | Address                | Access        | Description                                                    |  |  |  |  |  |  |

|------------------------|------------------------|---------------|----------------------------------------------------------------|--|--|--|--|--|--|

| MASTER/SLAVE SPI (SPI) | IASTER/SLAVE SPI (SPI) |               |                                                                |  |  |  |  |  |  |

| DATA                   | 0x41A00000             | R/W           | Transmit data (write) and receive data (read)                  |  |  |  |  |  |  |

| CFG                    | 0x41A00004             | R/W           | Master/Slave SPI configuration                                 |  |  |  |  |  |  |

| STS                    | 0x41A00008             | R/W           | Master/Slave SPI status                                        |  |  |  |  |  |  |

| UNIVERSAL SYNCHRONOUS  | ASYNCHRONOU            | S RECEIVER/TF | ANSMITTER 0 (USART0)                                           |  |  |  |  |  |  |

| DATA                   | 0x41B00000             | R/W           | USART0 transmit data (write) and receive data (read)           |  |  |  |  |  |  |

| CFG                    | 0x41B00004             | R/W           | USART0 configuration                                           |  |  |  |  |  |  |

| STS                    | 0x41B00008             | R/W           | USART0 status                                                  |  |  |  |  |  |  |

| UNIVERSAL SYNCHRONOUS  | ASYNCHRONOU            | S RECEIVER/TF | ANSMITTER 1 (USART1)                                           |  |  |  |  |  |  |

| DATA                   | 0x41C00000             | R/W           | USART1 transmit data (write) and receive data (read)           |  |  |  |  |  |  |

| CFG                    | 0x41C00004             | R/W           | USART1 configuration                                           |  |  |  |  |  |  |

| STS                    | 0x41C00008             | R/W           | USART1 status                                                  |  |  |  |  |  |  |

| l <sup>2</sup> C       |                        |               |                                                                |  |  |  |  |  |  |

| CFG                    | 0x41D00000             | R/W           | I <sup>2</sup> C configuration                                 |  |  |  |  |  |  |

| CTL                    | 0x41D00004             | WO            | I <sup>2</sup> C status and control                            |  |  |  |  |  |  |

| DATA                   | 0x41D00008             | R/W           | I <sup>2</sup> C transmit data (write) and receive data (read) |  |  |  |  |  |  |

| DATA_M                 | 0x41D0000C             | R/W           | I <sup>2</sup> C mirrored transmit/receive data                |  |  |  |  |  |  |

| ADDR_START             | 0x41D00010             | R/W           | I <sup>2</sup> C address to use for the transaction            |  |  |  |  |  |  |

| STS                    | 0x41D00014             | RO            | I <sup>2</sup> C status register                               |  |  |  |  |  |  |

| INT_STS                | 0x41D00018             | R/W           | I <sup>2</sup> C interrupt status register                     |  |  |  |  |  |  |

| MISCELLANEOUS          |                        |               |                                                                |  |  |  |  |  |  |

| REV_ID                 | 0x41F00050             | RO            | Revision ID                                                    |  |  |  |  |  |  |

| LOCK                   | 0x41F00060             | R/W           | Debug port lock                                                |  |  |  |  |  |  |

#### FLASH

Flash memory is directly addressable and may be used for system software or data storage.

The AXM0F343–64 MCU final word (address 0x0000\_FFFC) of the 64 kB of directly addressable memory is used as a LOCK word. See the Lock Control description for more detail on its use.

The AXM0F343–256 MCU final word (address 0x0003\_FFFC) of the 256 kB of directly addressable memory is used as a LOCK word. See the Lock Control description for more detail on its use.

Under normal operation, the flash block operates as if it were a ROM, providing single cycle read access via the AHB. Under software control, however, pages of the flash may be erased or programmed. These operations make read access to the flash memory unavailable until completed. If the CPU is executing from Flash, the processor will simply stall waiting for the AHB Ready signal from the Flash to return high. If the CPU is executing from RAM, the program/erase status can be read via the PGERDONE bit.

The registers used for programming and erasing the flash are mapped onto the APB.

AXM0F343-64 MCUflash is divided into 128 pages of 512 bytes each.

AXM0F343–256 MCU flash is divided into 256 pages of 2 kbytes each.

Each page may be independently erased, to allow for new content to be programmed. An erased address contains all 1s. Programming a word (or half word) can alter 1s to 0s, but cannot convert 0s to 1s. Only an erase can convert 0s to 1s.

To safeguard against inadvertent alteration of the flash content by errant code, each program/erase operation requires writing the keyword 0xA45B to the upper 16 bits of the FLASH CTL register. Reading the FLSH CTL register will always return all 0s for the upper 16 bits.

To program data into the flash, the starting address is written to the FLASH ADDR register, and a word, or half-word, of data is written to the FLASH DATA register. If half word programming is selected bits 15-0 of the FLASH DATA register will be programmed into the selected half word of the address. The PGM bit is then written to a 1 in the FLASH CTL register along with the half word selection, and the keyword 0xA45B in bits 31:16. The PGM bit will clear itself. When programming is complete, the PGERDONE bit in the FLASH CTL register will be high. If a full word, or the upper half of a word is programmed, the FLASH ADDR register will also automatically increment by 4 to allow for programming the next address in the flash. If the program interrupt is enabled, an interrupt will be generated when the PGERDONE bit is set. Programming a word/half-word in the flash requires 20 microseconds. The Flash controller will stall until the erase is complete. After the erase is complete the keyword should be written into the FLASH CTL register to unlock the Flash. If the page protection bit for that page is set, the programming will fail. If the protection interrupt is enabled, an interrupt will be generated immediately.

To erase a page of data, any address within the target page may be written to the FLASH ADDR register. The PGERASE bit is then written to a 1 in the FLASH CTL register, along with the keyword 0xA45B in bits 31:16 of the same register. The PGERASE bit will clear itself. When erase is complete, the PGERDONE bit in the FLASH CTL register will be high. If the erase interrupt is enabled, an interrupt will be generated when the PGERDONE bit is set. Erasing a page of data requires 10 milliseconds. If the page protection bit for that page is set, the erase will fail. If the protection interrupt is enabled, an interrupt will be generated immediately.

It is also possible to erase the entire user memory in the flash, returning the part to factory condition. This is done by writing a 1 to the MASSERASE bit in the FLASH CTL register, along with the keyword 0xA45B in bits 31:16 of the FLASH CTL register. A mass erase requires 10 milliseconds. The Flash controller will stall until the mass erase is complete. After the mass erase is complete the keyword should be written into the FLASH CTL register to unlock the Flash.

It is possible for application code executing from FLASH to perform a page erase, word, and half-word write. The FLASH\_EN bit in the PCLK\_EN register must be set prior to writing the PGERASE or PGM bit. Also it is best to bad the FLASH  $\rightarrow$  CTL write with NOP to make certain there are no FLASH controller/micro contentions upon exiting the FLASH ERASE/WRITE.

Flash Access Times:

Table 6.

| Flash Access Type      | Time  |

|------------------------|-------|

| Flash Read             | 40 ns |

| Flash Write            | 20 μs |

| Flash Page Erase       | 10 ms |

| Flash Full Macro Erase | 10 ms |

AXM0F343 MCU Flash Comparison:

Table 7.

|                   | AXM0F343-64 MCU   | AXM0F343-256 MCU |

|-------------------|-------------------|------------------|

| FLASH Size        | 64 kB             | 256 kB           |

| FLASH Size        | 128 x 512 B Pages | 256 x 2 kB Pages |

| Lock Word Address | 0x0000_FFFC       | 0x0003_FFFC      |

Flash Endurance:

Table 8.

| Flash Endurance Type | Minimum (–40°C to +85°C)                      |