## Development of a Trench isolated 50V technology on an SOI substrate

<u>'Remy Charavel<sup>1</sup></u>, Herbert De Vleeschouwer<sup>1</sup>, J. Baele<sup>1</sup>, P. Gassot<sup>1</sup>, E. De Backer<sup>1</sup>, M. Tack<sup>1</sup>

<sup>1</sup>On Semiconductor Westerring 15 9700 Oudenaarde, Email: Remy.Charavel@onsemi.com

Phone: +32-55332765 - Fax: +32-55332452

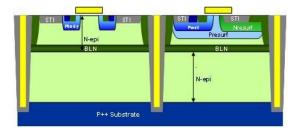

High voltage BCD technologies developed at ON Semiconductor entail vertical DMOS requiring an n-buried layer (BLN) to collect the drain current and a highly doped n-path from the BLN to the top silicon, called n-sinker to bring back the current to the surface. The n-sinker is integrated to the Deep Trench Isolation module (DTI) required to isolate high voltage devices.

The DTI module has been the object of careful process optimization on bulk substrate to minimize leakage and reduce the amount of silicon defects [1, 2, and 3]. To further improve isolation and latch-up performances, the DTI module has been transferred to SOI (Fig. 1).

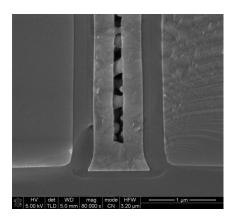

Feasibility of DTI without n-sinker on SOI has already been demonstrated with a filling made only of deposited oxide [4, 5] or of a bi-layer thermal oxide / polysilicon [6]. Adding an n-sinker to the sidewall of the DTI module is source of silicon defects, which can be reduced by filling the trench with a bi-layer deposited TEOS / polysilicon[7]. We demonstrated that defect free processing of DTI with n-sinker on SOI was possible using a bi-layer of thermal oxide, TEOS and polysilicon as filling.

For the purpose of the experiment a test vehicle has been processed on SOI and its quality was assessed by electrical measurements and physical characterization. On SOI, since the isolation is being ensured by the Buried Oxide (BOX) and not by a diode, the DTI processing can be limited to its upper part above the BLN. The etching down to the substrate is therefore avoided, as well as the hard mask it requires. Although processing is simpler and electrical performances are better, the module is very sensitive to liner oxide and sinker doping processing conditions with respect to defect generation.

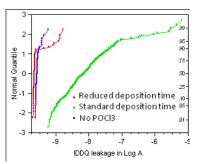

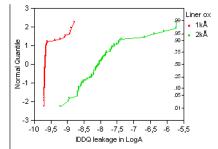

First of this critical processing steps, the N-sinker, is formed by liquid source diffusion using  $POCl_3$  as the Phosphorous source. The doping sequence starts with the conformal deposition of a phosphorus doped oxide, followed by a diffusion step where the phosphorous penetrates into the silicon. As seen in Fig. 2, long phosphorous deposition steps result in higher silicon defect. Next to destructive selective wet etching, drain quiescent current frames (IDDQ) can also be used to quantify accurately silicon defects. Fig 4 shows the response leakage of the IDDQ array for various POCl<sub>3</sub> splits. No sinker or lowly doped sinker yields no leakage while highly doped sinker results in high IDDQ leakage level, which is in line with the defect signature revealed by selective wet etching.

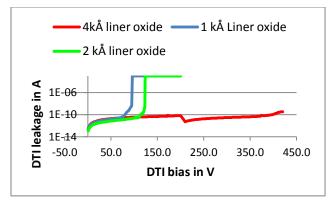

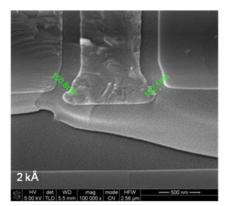

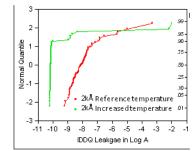

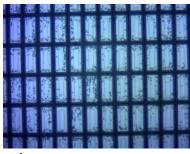

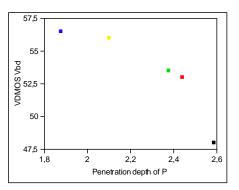

As depicted in Fig. 3, a thick liner oxide guarantees a high breakdown voltage of the DTI. For too thin liner oxide, the breakdown voltage decreases drastically due to oxide thinning at trench bottom (Fig.5). Unfortunately, increasing liner oxide thickness yields too many silicon defects if oxide is grown at reference temperature (Fig. 6). A way to overcome the appearance of silicon defects is to grow the liner oxide at higher temperature. Fig. 7 and 8 shows that defects can be avoided even for a 3 kÅ liner oxide when grown at higher temperature. This beneficial effect of high temperature can be attributed to the oxide viscosity and generated stress which decreases with increasing temperature [8, 9]. However, a trade-off has to be found between increased thermal budget necessary to avoid silicon defects and excessive sinker diffusion induced by this thermal budget. Indeed, as seen in Fig. 9, if sinker diffuses too much towards the active area, the breakdown voltage of VDMOS drops due to interaction with the lateral termination of the device. A way to overcome the too high thermal budget while enhancing the breakdown voltage of the DTI module and avoiding generation of silicon defects is to deposit a TEOS layer on a thin liner oxide grown at reference temperature. As seen in Fig. 10, the deposited TEOS is very conformal and compensate the liner oxide thinning at trench bottom.

We demonstrated so far that fabrication of defect free DTI trenches with high breakdown voltage was possible. Final paper will present an optimized DTI module, combining high DTI isolation capability, low diffusion of sinker and defects free silicon. Two processing options are being investigated; reducing the initial sinker doping to keep sinker diffusion under control despite a high thermal budget required to grow a thick liner oxide at high temperature or combining a thin thermal oxide grown at low temperature with a TEOS deposition to enhance dielectric thickness.

Acknowledgements: This work was performed in the framework of the European project SmartPM.

[1] F. De Pestel et al., "Development of a 50V 0.35 μm Based Smart Power Technology Using Trench Isolation", ISPSD 2003, 2003.

[2] H. De Vleeschouwer et al., "Leakage phenomena in Trench isolation technologies: study of process and layout sensitivities", ARCSIS, 2007.

[3] I. Mica, "Crystal Defects and junctions in the evolution of device fabrication", J. Phys Cond. Matter 14, pp. 13403-13410, 2002.

[4] T. Nitta et al., "Wide Voltage Power Device Implementation in 0.25 μm SOI BiC-DMOS", ISPSD, pp. 1-4, 2006.

[5] A. Hölke, , "A 200V Partial SOI 0.18µm CMOS technology ", ISPSD, pp. 257-260, 2010.

[6] L. Clavelier, "Deep trench isolation for 600V SOI power devices", ESSDERC, pp.497-500, 2003.

7] X. Cao, "Control of Crystalline Defects in Trench Isolated Thick Film SOI for High Voltage Smart Power ICs", Electrochemical Society Proceedings, vol. 29, pp.103-111, 2001.

[8] D.B. Kao t al., "Two Dimensional Thermal Oxidation of Silicon – Modeling Stress Effect in Wet Oxides", IEEE Transaction on Electron Devices, Vol. 35, n°1, pp. 25-37, 1988.

[9] P.M. Fahey et al., "Stress Induced Dislocations in Silicon Integrated Circuits", IBM Journal Research Development, Vol. 36, n°2, pp.158-182, 1992.

Bulk version

SOI version

(a) Long POCl<sub>3</sub> deposition step + standard

diffusion

+ standard (b) Reduced POCl<sub>3</sub> deposition step + standard diffusion

Figure 1: Schematic of the high voltage technology on bukl and SOI substrates

Figure 3: Leakage of IDDQ frame in function of POCl<sub>3</sub> deposition time

Figure 2: Silicon defect generation in function of POCl<sub>3</sub> processing. Long deposition step (a) yields silicon defects while reduced deposition step (b) avoid defect formation

Figure 4: DTI breakdown voltage in function of liner oxide thickness

Figure 5: Oxide thinning at trench bottom

Figure 6: IDDQ leakage in function of liner oxide thickness (reference temperature)

Figure 7 : IDDQ Leakage in function of liner oxide temperature

3 kÅ liner oxide at reference temperature

Figure 8: Defect generation in function of liner oxide temperature growth.Figure 9: N-sinker diffusion depthLow oxidation temperature (a) yields silicon defects, while high oxidationversus VDMOS breakdown voltagetemperature (b) results in defects free structuresversus VDMOS breakdown voltage

Figure 10: Reduction of dielectric thinning by depostion of a TEOS layer