エンタープライズサーバおよびクラウドデータセンタ電力のための「80+Titianium」、ならびに外部電源アダプタのためのEU CoC Tier2などの省エネルギーのイニシアティブは、電力設計者が設計においてより優れた効率化を図るために、GaNスイッチ技術の選択を先導しています。しかし、GaNは、既存のシリコン技術をそのままで置き換えられるものではありません。最大のメリットを得るためには、ドライブと基板レイアウトをこの新しい技術に合わせる必要があります。

GaNスイッチとシリコンスイッチの比較

GaNは、デバイスの容量が小さく、逆回復電荷を伴わずに逆導通(第3象限)することができるので、高速です。これは、ハードスイッチアプリケーションでは大きなメリットです。その結果、損失はより少なくなりますが、いくつかの欠点があります。デバイスはアバランシェ電圧定格を有しておらず、ゲートドライブは非常に重要であり、他の点では同条件のSiデバイスの場合の+/−20Vと比較して、通常の絶対最大電圧定格は+/−10Vです。エンハンスメントモード(E-mode)のGaNはノーマリーオフのデバイスであり、そのゲートターンオンスレッショルドもSiより低く、3.5Vに対して約1.5Vです。重要なこととして、より高い電力密度と高い信頼性でより低い損失という期待される利点を達成することは、堅牢な保護機能をで最適化されたゲートドライブ回路に依存することです。

性能の鍵となるGaNのゲートドライブ

完全なエンハンスメントのために、E-mode GaNスイッチは、約5Vまでドライブされる必要がありますが、それほど高くはありません。絶対最大制限値を超えない限り、ゲート回路で消費される電力は、ゲートドライブ電圧と周波数に比例します。デバイス容量とゲート電荷が小さいと、平均ドライブ電力が非常に低くなり得ます。しかし、スイッチングはナノ秒のオーダーなので、ピーク電流はアンペア単位で高くなる可能性があり、したがって、ドライバ回路は速度に整合する必要がありますが、それでもかなりの電流を供給することができます。

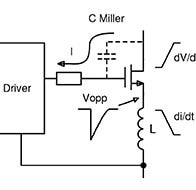

理論的には、GaNデバイスはVGS=0で確実にオフになりますが、ドライバからスイッチソースに戻る閉じた「ケルビン」接続がなされない場合、結果として生じる接続インダクタンスは、デバイスがスイッチするときに電圧スパイクを引き起こします(図1)。これはゲートドライブとは反対に、よくてドライブ電圧マージンを低減し、最悪の場合にはスプリアスターンオンを引き起こしてダメージを与える結果をもたらす可能性があります。この影響を打ち消すためにゲートを負にドライブすることができますが、注意深いレイアウトおよびケルビン接続を容易にするドライバを用いて回避することができます。「ミラー」キャパシタンスは、同様の効果を引き起こすことができますが、GaNでは、これはごくわずかです。

図1: ソースとゲートのドライブに共通のインダクタンスにより過渡電圧が発生

ハイサイドゲートドライブの課題

いくつかの変換トポロジーは、ゲートドライブのリターンが高電圧のスイッチングノードである「ハイサイド」スイッチを使用します。ドライバはレベルシフトしなければならず、出力から入力へのdV / dtの影響を受けないようにする必要があります。これは、GaNでは100V / ns以上になる可能性があります。また、この状況では、ローサイド信号とハイサイド信号が一致し、最小のデッドタイムを可能な限り短くしながら、壊滅的な「シュートスルー」と重ならないように、ドライバを通る伝搬遅延を適切に制御する必要があります。ローサイドドライブであっても、ドライバの出力段から入力側へ戻るノイズのカップリングを回避するために、信号と電源のグランド間のレベルシフトを可能にする必要がある場合があります。これは、異常動作や最悪の場合はデバイス故障を引き起こす可能性があります。

アプリケーション例 : アクティブクランプ・フライバック

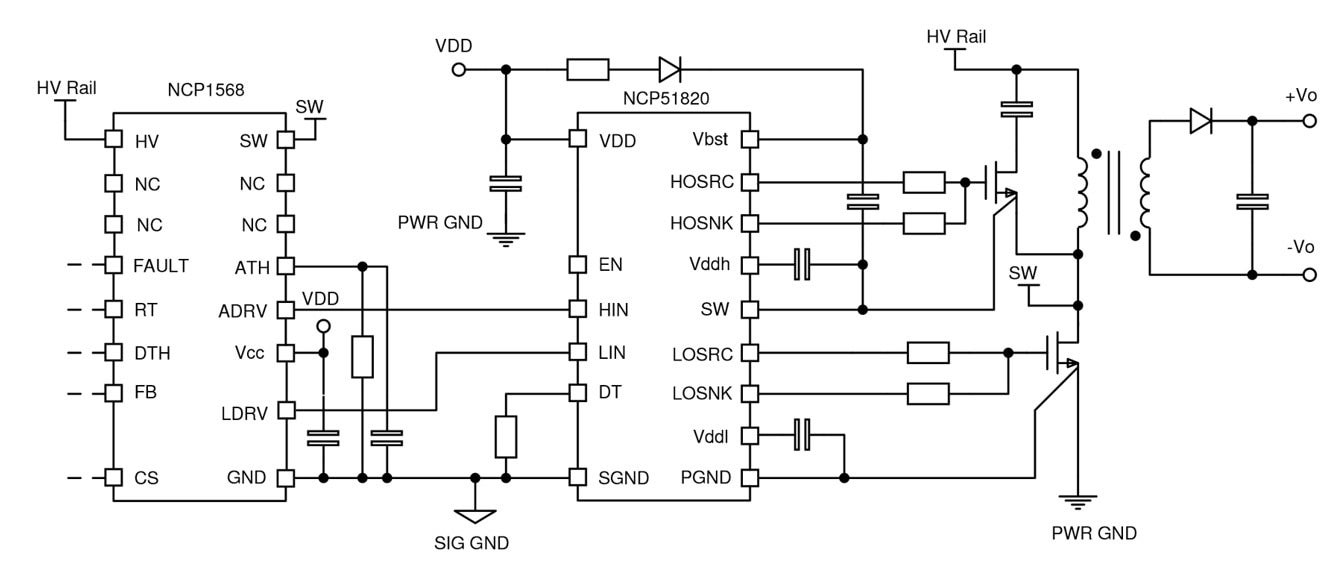

図2: GaNベースのアクティブクランプ・フライバックコンバータの概要

図2に、オン・セミコンダクターのNCP51820 GaNゲートドライバとNCP1568アクティブクランプ・フライバックコントローラを示します。このドライバは、E-mode GaNを制御するのに最適なハイサイドおよびローサイド出力に対して調整された+5.2V振幅を有するゲートドライバを備えています。また、革新的なジャンクション絶縁技術により可能となった、-3.5V〜+ 650Vのハイサイドコモンモード電圧範囲と、ローサイド用の-3.5〜+ 3.5V、および200V / nsの耐性を備えています。ローサイドドライブのレベルシフトを行うことで、ローサイドデバイスのソースに電流検出抵抗がある場合は、ケルビン接続が容易になります。ドライバ波形の立ち上がり時間と立ち下がり時間は1nsであり、最大伝搬遅延は50nsです。

別々のソースおよびシンク出力が提供されているので、ターンオンおよびターンオフのエッジレートを個別に制御して、最良のEMI/効率を得られます。

アプリケーション例: LLCコンバータ

LLCコンバータ(図3)の特徴は、ドライブ波形がそれぞれ50%のデューティサイクルであることです。従って、オーバーラップが生じないようにデッドタイムを制御することが重要です。

図3: GaNベースのLLCコンバータの概要

オン・セミコンダクターのNCP51820ドライバは、ゲートドライブがオーバーラップしないことを保証します。また、イネーブル入力および電源電圧の低下と温度超過に対する包括的な保護機能も備えています。これは、GaNデバイスゲートへの短い、低インダクタンスの接続を可能にする、4×4mm 15リードのPQFNパッケージで提供されます。

基板レイアウトが重要

どのようなアプリケーションにおいても、目標性能を達成するためには基板レイアウトが非常に重要です。ゲートドライバのループは最小限に抑え、整合させる必要があります。ドライバとGaNデバイスは、使用するPCBとグランド/電源プレーンの同じ側に配置する必要があります。

まとめ

GaNスイッチは、動作信頼性とともに、効率と電力密度における期待された利得を達成するために、ゲートドライブ回路の慎重な設計を必要とします。注意深いレイアウトとともに、オン・セミコンダクターのNCP51820のような、ハイサイドドライブおよびローサイドドライブ用の多数の機能を備えた専用ドライバにより、GaNデバイスが最良の性能を発揮することを確実にします。

NCP51820高速ゲートドライバの詳細をご覧ください。